发布时间:2010-11-14 阅读量:1343 来源: 我爱方案网 作者:

其次,针对当前网络带宽还不够,无线通信信道误码率较高的情况,稳定的低码率视频信号的需求一直都是必须和必要的

因此,将H.264的先进技术和稳定的媒体处理器相结合,实现高效的媒体通信平台有着一定的工程意义和市场价值。

H.264简介H.264是ITU-T和ISO/IEC联合制定的最新编码标准,它最先由ITU-T于1997年提出,目标是提出一种更高性能(相对于当时的H.263)的视频编码标准。相对于其它标准,H.264具有以下特点:

1. 低码率,高质量

在相同质量的情况下,H.264相对于H.263的Baseline可以节约40%~50%的码率。

2. 广阔的应用范围

H.264的不同Profile既可以应用于有严格时延限制的实时通信中,也可以应用于对时延要求不高的其他应用中(视频存储、流媒体等等)。

3. 鲁棒性

H.264在设计时,针对分组交换网如Internet中的分组丢失和无线网络中比特误码都提出了相应的工具,使得H.264在这些网络中传播时具有更强的抗误码性能。

4. 对各种网络的友好性。

H.264中增加了NAL层,负责将编码器的输出码流适配到各种类型的网络中,从而提供了友好的网络接口。H.264之所以能够达到以上性能,是因为采用了以下一些先进的技术:

首先是帧内预测编码,充分利用图像空域相关性,来降低码率。共有13种预测模式(4×4块大小9种预测模式,16×16块大小4种预测模式),这在以往标准中是没有的。

其次采用新的运动估计方法。H.264有7种块匹配模式,编码时对其逐一计算,选择最优。例如较为精细的部分采用4×4块大小,不运动的背景可以采用16×16块大小等等。以往标准只有固定的一种或两种块大小模式。H.264采用多帧参考,最大限度利用实域相关性。参考帧可以从1帧到15帧,以往标准都是单帧参考。还有采用1/4或1/8精度的亚象素运动估计,以往标准至多采用1/2精度亚象素搜索,而且不是必选选项。为了消除视频编码中常出现的块效应,H.264使用了去块效应滤波器。

它还采用整数DCT变换,以提高变换速度,采用CAVLC,CABAC等新的熵编码方法以提高编码效果。

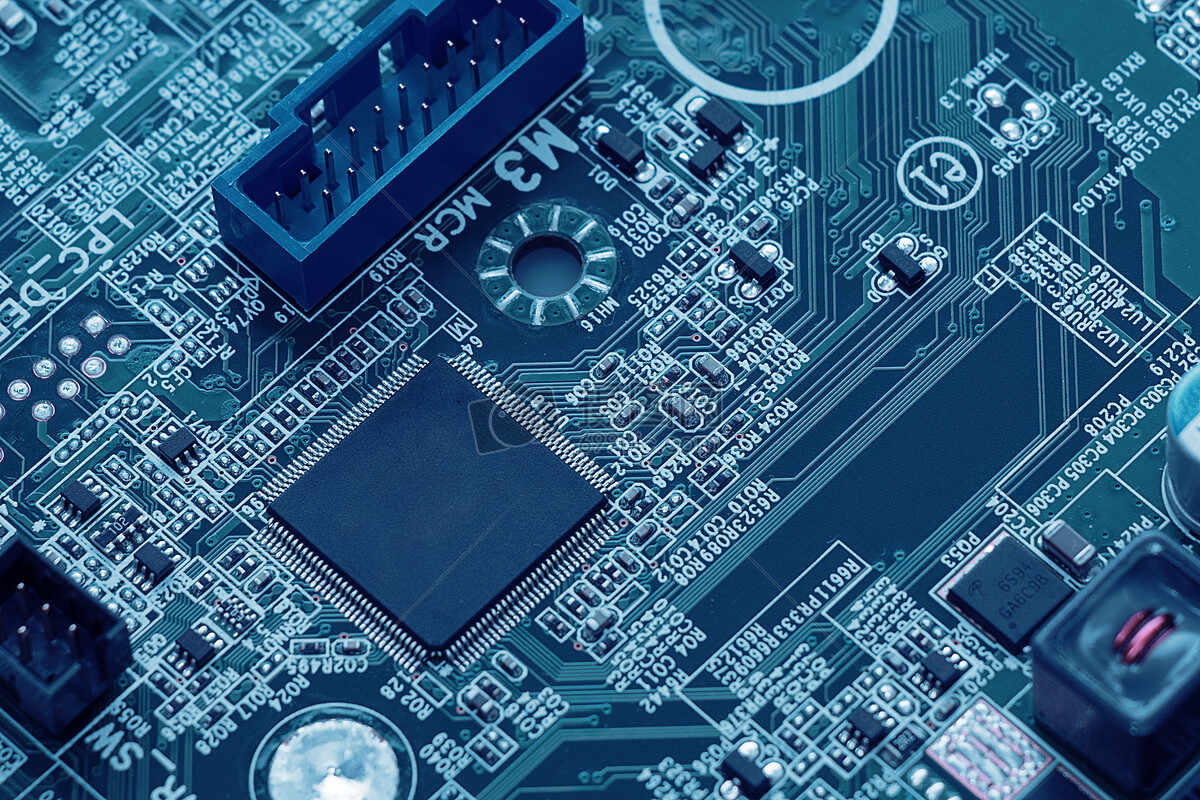

NVDK开发平台介绍

NVDK是TI的第三方ATEME公司推出的基于TI的C64系列DSP评估开发套件,是一套适用于图像、视频信号处理的高速DSP开发平台。该套件为诸如视频基础设施及网络化视频设备等高级视频应用制造商提供了方便,提高了数字视频应用项目的开发速度。

NVDK的核心是一块C6416DSP,主频600Mhz,处理能力达到4800MIPS。它具有64个独立通用寄存器,1M字节的片上内存,具有64位和16位片外内存接口各一个。它还具有丰富的DMA通道,大大缓解了CPU的运算压力。此外,C6416支持8,16,32,40,64位数据读写及运算,具有丰富的媒体处理指令,如一条指令对4个字节的数据进行加、减、乘、求绝对值、点乘等运算,方便进行媒体处理开发。

此外,NVDK板上还有丰富的音视频接口,并提供相关的视频捕获,格式转换,视频播放等函数,大大方便我们的工作。

H.264编解码器在DSP上的实现与优化

将H.264在DSP上实现与优化,需要经过以下几个步骤:PC机端算法实现及优化,代码移植,DSP端代码优化。下面就着几个方面逐一进行介绍:

1. PC机端算法实现与优化。

我们选取ITU-T公布的JM6.1e参考软件作为我们的优化对象,目标是实现一个base-line profile的实时编解码算法。但是JM6.1e代码复杂,冗余度很大,需要在PC机端对其进行较大调整,涉及工作有:去除冗余代码、规范程序结构、全局和局部变量的调整和重新定义、结构体的调整等。

2. 代码移植

代码移植,就是将在PC端跑通的程序,移植到DSP端,使其能够初步运行。需要考虑的问题主要是一些内存分配,语法规则等问题。

3. DSP端代码的优化

通过把PC机H.264代码DSP化,可以在DSP上实现H.264的编解码算法,但是,这样实现的算法运行效率很低

,因为所有的代码都是由C语言编写,并没有完全利用DSP的各种性能。所以必须结合DSP本身的特点,对其进一步优化,才能实现H.264视频解码器算法对视频图像的实时处理。

代码的优化分为三个层次:项目级优化,算法级优化,指令级优化。

* 项目级优化 项目级优化,是对项目的整体优化,主要手段有以下几点:

首先是利用CCS编译器提供的优化功能,对优化选项进行选择和配置,如打开O-3选项等。

其次对程序结构进行调整,对不适合DSP执行的语句进行改写,以提高代码的并行性。

最后是对内存进行合理分配,因为DSP资源有限,我们把一些常用数据,如全局变量,程序等数据分配到访问速度高的片内内存,把占用空间较大的数据分配在片外,如帧存等。

* 算法级优化

是利用H.264的自身特点,提出快速高效算法,从算法上挖掘潜力,提高运行速度,达到优化目的。这部分工作主要集中在编码器优化方面。

视频编码中,运动估计部分是运算量最大的一块,研究显示,对于H.264,单帧参考,运动估计占总运算量的70%,5帧参考,这个比例能达到90%,因此,提出有效快速的运动估计算法非常有必要,我们通过研究提出了基于预测和早停止技术的运动估计算法,主要方法是利用周边邻块对当前块运动矢量进行预测,并设定自适应阈值,使搜索提前停止。我们提出的算法,在搜索窗32时,每块平均搜索点数3-4个左右,和全搜索算法的4225余个点相比,提高速度1000多倍。和一些经典快速算法相比,优势也很明显, H.264算法中,亚象素运动估计采用全搜索,1/4精度下,需要搜索16个点。我们提出了自己的亚象素快速搜索算法,平均搜索点数7个,节省运算量60%以上。我们提出的新算法提高编码速度很明显,而且质量也较好,PSNR损失不到0.06dB,码率增大2%左右。这对于运动估计算法基本可以忽略不计。

此外,我们针对帧间编码7中块大小匹配模式,以及帧内预测13中模式太过复杂,运算量太大的问题,提出了我们自适应模式选择算法,不需要将所有模式全部计算,就能找到一种相对最优的模式。这些算法,都大大提高了代码的运行速度,在速度与质量上达到较好的折中。

* 指令级优化

如果上述优化方法无法达到实时要求,就需要进行指令级优化了,主要手段有。

* 循环拆解,将C语言中的for循环打开,排流水线,提高并行性

* 调用系统提供的丰富的内联函数

* 调整数据结构,将需要大规模访问的数据,在内存中将它们放置在一起,方便DMA机制的访问,或并行指令的处理,如插值函数模块。

* 将耗时函数抽取出来,用线性汇编改写,充分利用丰富的媒体处理指令【5】,最大限度的利用DSP的并行性。例如,运动估计中频繁调用的SAD计算,是对相应象素点做差,并对残差场求绝对值和的计算。原始算法是对每一对象素点分别求差,再对其绝对值累加。我们对其进行了线性汇编的改写,使用了SUBABS4(一次对两对4字节数据做差并求绝对值),DOTPU4(一次对两对4字节数据做内积),LDW\LDNW(一次读取4字节数据)等指令,使代码并行性有了很大提高。对16×16的块来说,优化前需要指令1000余条,优化后,200条就足够了。 我们充分利用系统并行性,对耗时函数进行汇编语言改写,涉及函数有DCT变换,反DCT变换,整象素运动估计,亚象素搜索,帧内编码函数,插值函数等,效果明显。

算法性能的评测及前景展望

在NVDK C6416环境下,测试了编解码器算法,对QCIF测试序列,编码器40_50帧/秒的编码码速度,解码器达到50_60帧/秒的解码速度,远远达到了实时性解码的目的。

因为代码的兼容性和可移植性,我们可以把在C6416上实现的编解码算法移植到TI公司推出的媒体处理专用芯片TMS320DM642上,利用其丰富的媒体处理接口和协处理器,实现更好的性能。

三星开启内部审查,严查员工收受不当回扣行为

长江存储正逐渐成为消费电子领域(包括PC与智能手机)为数不多的稳定供应来源。

据苏州高新区发布消息,12月18日,维谛技术华东研发制造基地战略合作项目签约仪式在苏州高新区举行。

由于半导体短缺,日本汽车大厂本田宣布实施短期停产与减产措施

近日,工业和信息化部部长李乐成在北京会见美国超威半导体公司(AMD)董事会主席兼首席执行官苏姿丰。