【导读】直接数字式频率合成器以其极高的频率分辨率、极短的频率转换时间、相位精确可调、设备结构简单、易集成、体积小及成本低等优点,在高分辨雷达系统、宽带扩频通信系统以及现代测控系统中得到广泛的应用,我们详细介绍一款方案。

了便于信息的采集、处理和操作控制,常常要求信号源基于PC机平台设计。PC机内部有两种常用的总线,即PCI总线和ISA总线。ISA总线接口关系简单.操作控制方便,能够满足系统要求,是比较理想的DDS与计算机的接口总线。随着电子系统复杂性的不断增加,单路DDS已经不能够满足系统需求,多路DDS系统的设计开始成为研究的热点。

1、系统工作原理

图1是某自动测试系统的工作原理框图。图中的高稳定度频率基准为整个系统提供频率为50MHz的参考时钟。系统的控制命令由计算机发出,经过ISA总线传输,送到FPGA进行缓存、译码,同步控制三路DDS产生需要的信号。其中,DDS1的输出信号为初始相位可变,脉冲宽度、脉冲周期、脉冲个数等由计算机编程设定的射频脉冲序列。脉冲的载波频率在fT=2lMHz附近可调。该射频脉冲经过功率放大、低通滤波后,在高频开关的控制下发射出去。接收到的反射回波由高频开关选通,与DDS2产生的20MHz第一本振fLO1混频,得到频率为1MHz的中频脉冲调制正弦信号。

为了便于信号处理,该系统对各路DDS输出信号的时间关系提出了严格的要求:

(1)相位检波器的两路正交参考信号相位应严格控制在90°相差上,以保证正交检波器的性能。

(2)其初始相位可以通过计算机控制调整。

(3)DDS2的输出信号和DDS3的I支路输出信号必须同步,以保证在DDS3同相支路上的信号相位与中频信号的相位保持同步;同时Q路信号必须保持相位的正交。

(4)每个射频脉冲周期,各路DDS输出信号的初始相位严格同步,保证回波信号的相参积累。

2 多路同步设计

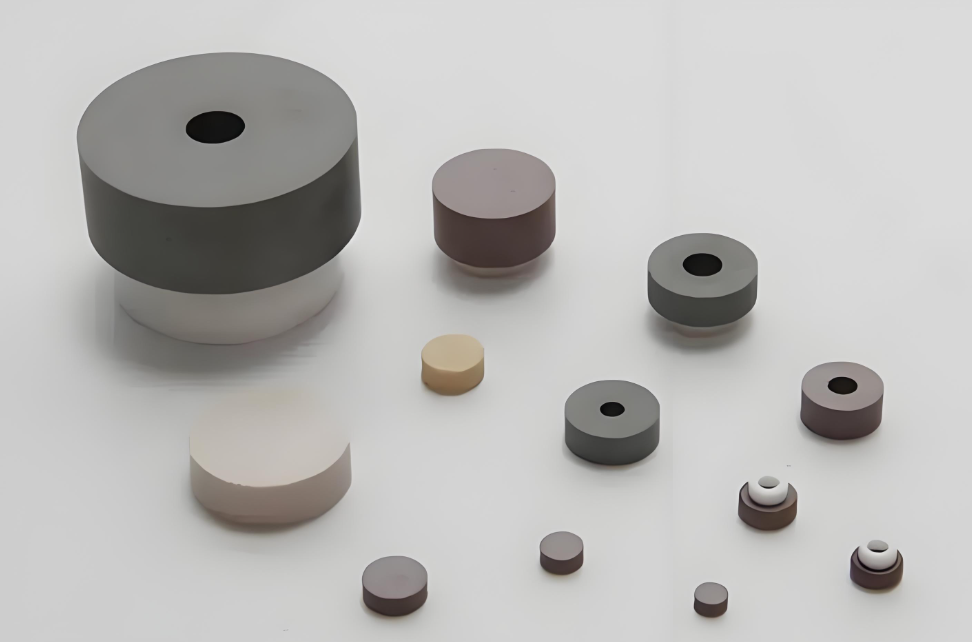

图3是该自动测试系统的数据采集、多路DDS同步单元的实现框图。经过相位检波、低通滤波的I、0两路信号输入到该单元电路中,经OP-07放大、AD976采集后,再经FPGA由ISA总线送入到计算机中。OP-07具有低偏移、高开环增益的特点,适合于高增益的测试系统应用。AD976是采样速率为200ksps的高速16位低功耗模数转换器。FPGA芯片采用Ahera公司的ACEX系列芯片EPlK50,实现ISA总线与三路DDS及数据采集的接口。其灵活的可重新配置特性为实现接口电路提供了极大的方便,片上集成有4OKbit的RAM,便于缓存计算机的控制信息。DDS芯片选择美国模拟器件公司的AD9854。它的相位累加器为48位,利用片上PLL可实现4~20倍的可编程倍频,内部最高时钟可达300blHz,尤为突出的优势在于具有100MHz的高速并行配置接口,内置最大相位误差小于1°的I、Q两路的DAC输出,便于产生lMHz的正交信号。对于该自动测试系统,各路DDS之间的同步关系是电路设计的核心问题。AD9854芯片本身没有同步信号,要实现各路的精确同步,必须对电路进行优化设计。为分析方便,分别从参考时钟、刷新时钟和内部锁相倍频三部分进行讨论。

成功的同步设计要求各路DDS的参考时钟之间的相位差最小。参考时钟边沿的时间差会使各路DDS输出信号产生相应比例的相位差。参考时钟的边沿抖动要足够小,上升/下降时间要短,以免增加时钟信号的相位误差。

数据采集与多路DDS单元电路首先把外部送来的50MHz高精度、高稳定度的正弦信号转换成方渡,送给各路DDS作参考时钟。时钟转换功能利用1:4的PECL时钟分配器SYl00EL15实现。ECL电路是现有各种实用数字逻辑集成电路中速度最快的一种,也是目前惟一能够提供亚毫微秒开关时间的实用数字逻辑电路。SYl00EL15最高可以工作在1.25GHz频率上,器件间的最大偏斜为200ps,单个器件的最大偏斜为50ps,时钟均方抖动仅为2.6ps,上升时间介于325ps和575ps之间。AD9854的参考时钟能够兼容PECL逻辑。射频信号在长线传输过程中,为了抑制由此产生的反射和串扰,SY100EL15的输出与AD9854参考时钟之问的PECL逻辑电路必须良好地匹配。图4的匹配方式是一种比较好的方案。

刷新时钟

AD9854芯片引脚中与配置内核密切相关的信号除了数据线、地址线、写信号以外,还有刷新时钟。写信号的作用是将I/O口上的数据传送到AD9854芯片内部的缓冲区中,而刷新时钟则用于配置AD9854内核的相应寄存器。刷新时钟引脚既可以作为输入信号,工作于外部刷新模式;又可以作为输出信号,工作于内部刷新模式。鉴于多路同步原因,通常工作于外部刷新模式。刷新信号的时序如图5所示。

锁相倍频

根据数模转换的数学模型,DDS输出信号的频率通常不得超过系统时钟频率的40%。以50MHz作为参考时钟产生频率为20MHz的信号会给滤波带来困难。AD9854内部集成了锁相倍频电路,可以将50MHz的参考时钟倍频至200MHz。片上锁相倍频电路带来的问题是环路建立时间会随着AD9854及片外环路滤波器的器件不同而产生差异。这将导致在锁相环路的建立过程中,送给AD9854相位累加器的系统时钟周期数目无法准确预测。

因此在环路建立过程中,相位控制字的值必须为零以避免相位累加器的值不断累加。DDS芯片内部集成锁相环路的建立时间典型值约为400μs。为了保证各路DDS的同步,在起始10ms让AD9854输出的频率控制字和相位控制字始终为零。10ms以后,才启动AD9854的输出相位累加过程。待PLL建立起来以后,再改变各路DDS芯片相应的控制字。