发布时间:2014-02-19 阅读量:2021 来源: 发布人:

USB3.0标准

为了加强USB 的性能和竞争力,USB 联盟推出了新的USB 3.0SS(SuperSpeed)标准。该标准使用两条差分链路实现了全双工通讯,速率达到了5.0Gps,不但高于1394b 标准,与eSATA 相比也同样具有竞争力。

USB3.0 在2.0 的基础上新增加了2 对差分链路,专门用于传送SS 差分信号。主机侧接口的机械特性和USB 2.0 兼容,而设备侧使用了新的接口形式,以容纳新增的两对差分信号线。USB2.0 接口的B 型连接器可以插入USB 3.0 的设备端,此时设备工作于USB 2.0 模式下;但USB 3.0 的B 型连接器无法插入USB 2.0的设备端。

除此以外,USB 3.0 的总线供电能力达到1A,使其可以用于移动硬盘等耗电量较大的设备,而不必另外配备外接电源。

CYUSB3014 芯片简介

CYUSB3014 是USB 业界的领头羊Cypress 公司出品的USB3.0 控制器,该款控制器集成了200MHz 的ARM9 控制器、512K 字节的RAM和USB 3.0物理层,具有可编程的100MHz GPIF II接口。

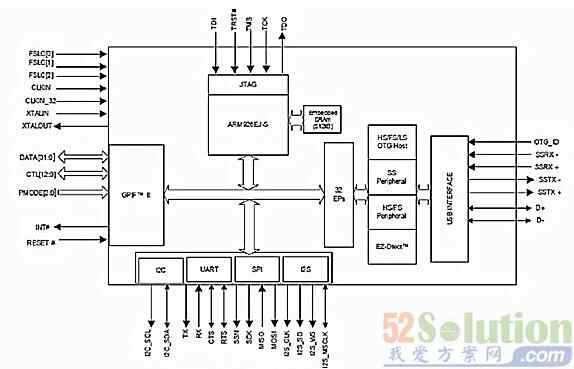

图1 是该芯片的逻辑框图,该芯片可用于数字摄像机、数据采集、测试测量设备等多个领域。

图1 CYUSB3014逻辑框图

系统硬件设计

本系统中,使用了一片AD6644 作数据转换。这是AnalogDevice 公司生产的14 位高速ADC,最高采样速率达到40Msps。整个系统的功能框图如图2 所示。

图2 系统框图

上图中,传感器将外部信号变换为电信号;放大滤波部分将传感器输出的微弱电信号进行放大、滤波处理,以去除外部干扰;AD6644 在FPGA 的控制下对放大滤波后的信号进行采集和转换;FPGA 读取AD 输出,并按照CYUSB3014 的GPIF II 接口规范将该数据写入芯片内部的FIFO.此外,FPGA 还可以根据当前信号特性调整放大滤波电路参数,以获取更优的信噪比。

GPIF II 接口与FPGA 程序设计

在整个硬件系统中,FPGA 与CYUSB3014 之间的数据传输速度是决定整个系统性能的关键。Cypress 在GPIF 的基础上设计 了可编程GPIF-II 接口,该接口可工作于主控或从属方式,支持32 位数据总线,接口频率最高可达100MHz,有异步和同步两种时序。在本系统中,为了达到更高的数据传送效率,根据GPIF-II 接口时序,编写了相应的FPGA 程序,实现了在FPGA 和CYUSB3014之间的高速数据传输。实测结果表明,FPGA 和CYUSB3014 之间的数据传输速度最高达到了200Mbytes/s,完全满足本系统要求。下文是数据传输状态机的部分代码:

USB 固件设计

CYUSB3014 集成了一片ARM9 核心的处理器,完成USB 初始化、枚举、数据传输管理等工作。固件开发使用开源的gcc 编译器和Eclipse 集成开发环境,下面是用于管理数据传输的部分代码:

上位机驱动和软件设计

Cypress 提供了基于WDF 的驱动程序模块,WDF(WindowsDriver Foundation)是microsoft 推行的驱动开发框架,用来替代之前的WDM 框架。WDF 框架对WDM 进行了封装和继承,与WDM相比,WDF 框架的驱动开发更简单方便,尤其是简化了电源管理和PNP(Plug and play)方面的工作量。根据该系统的实际需要,对驱动代码进行了修改并编写了应用程序,能够稳定可靠地采集数据,表明该系统满足了预期的设计要求。

结语

高速实时数据采集系统的设计方案,首先对传感器输出信号进行放大滤波处理,然后将其转换为数字信号。实践证明,USB 3.0 在USB 2.0 的基础上大大提高了数据传输速率,实时性也有很好的增强,能够满足高速实时数据采集的要求,在数据采集和测试测量领域必将大显身手。

紫晶存储犯欺诈发行证券罪,判处罚金人民币3700万元;公司实际控制人郑穆、罗铁威及原财务总监李燕霞等10名核心管理人员,全部被判处有期徒刑,刑期最高达七年六个月。

近日,日产汽车和总部位于英国的自动驾驶初创公司Wayve签署协议,合作开发基于人工智能的驾驶辅助系统。

京东开启招聘存算一体芯片设计工程师计划,薪酬高达“40K-100K*20薪”

日本芯片制造商铠侠(Kioxia)计划于2026年在其岩手县晶圆厂开始生产新一代NAND闪存芯片。

一系列诉讼指控芯片制造商英特尔、AMD及德州仪器公司,未能有效阻止其技术被用于俄罗斯制造的武器。