简介

采样保持(THA)输出噪声有两个关键噪声分量:采样噪声和输出缓冲放大器噪声。本文将重点探讨这两个分量。

采样噪声分量

噪声的第一个分量是采样过程中产生的采样噪声,它用外差法将THA的前端噪声转化到频域的每个奈奎斯特区间中。整个前端带宽产生的噪声是在每个时域样本中捕获,然后将该噪声大致均匀地分布在每个奈奎斯特区间上。此噪声由前端热噪声和采样抖动噪声组成,无法被滤除,除非在输出端使用低通滤波器转折频率来显著降低奈奎斯特带宽。通常不使用这种滤波,因为它会损坏时钟速率所提供的可用带宽,并导致输出波形的建立时间性能降低。

输出缓冲放大器噪声分量

噪声的第二个分量是THA输出缓冲放大器噪声贡献。THA不会对此噪声采样,但滤波可以降低此噪声。可以承受的输出滤波量取决于所用特定时钟频率的建立时间要求。关于容差限制的大致原则是输出路径的带宽(包括模数转换器(ADC)输入带宽)至少为时钟速率的2倍,以支持下游ADC所采样的THA波形的精确(例如线性)建立。高速ADC的输入带宽通常在2倍时钟速率指标附近;因此,使用高速ADC时通常不需要额外的滤波。

采样放大器的噪声密度

与常规非采样放大器不同,THA频域中的有效等效输入噪声谱密度取决于模数转换之前的输出滤波带宽。出于这个原因,采样器件通常不会用这些项来指定噪声,因为实际输出噪声是采样输入缓冲器噪声的复杂函数,其将整个输入带宽中的噪声混叠到第一奈奎斯特区间,输出缓冲放大器噪声响应输出限带的方式与常规放大器相似。采样系统的重要指标量是所保持输出样本中的时域输出噪声(参见HMC661LC4B数据手册),因为ADC会转换此输出噪声。

折合到输入端的频域噪声密度最好通过下式确定:输出时域采样噪声除以输入采样带宽与π/2的乘积的平方根。

单极点带宽和输出时域噪声相同时,该定义给出的折合到输入端噪声密度与单位增益连续波(CW)放大器(未采样)相同。之所以有π/2,是因为单极点低通传递函数的有效噪声带宽为BW3dB×π/2。对于没有输出限带的HMC661LC4B(例如输出缓冲放大器的全部7 GHz带宽),当使用1.05 mV rms时域采样噪声和18 GHz 3 dB输入带宽时,此噪声带宽对应于约6.2 nV/(√Hz)的等效输入噪声密度。由于热本底噪声为0.64 nV/(√Hz),所以有效噪声指数约为19.7 dB。此噪声指数很高,这是因为THA中有好几级,所有级均以单位增益工作,故每级都会增加噪声。

非采样放大器的噪声密度

就等效输入噪声性能而言,有效采样噪声指数的这种定义对普通非采样放大器是一个合理的比较。这并未考虑采样引起的噪声折叠,而典型混频器噪声指数定义可能会使用噪声折叠。要获得混频器噪声指数定义,须添加一个噪声折叠修正系数,它由输入采样噪声带宽与奈奎斯特带宽的比值给出,如下式所示:

NFCORRECTION = 噪声指数采样折叠校正 = 10log(BWN_INPUT/(fCLK_TH/2))

其中,BWN_INPUT表示输入采样带宽的有效噪声带宽。

例如,当HMC661LC4B以4 GHz时钟速率工作时,噪声折叠(18 GHz×π/2)至2 GHz的奈奎斯特区间所导致的额外降级是由混频器定义的,噪声指数额外降低约11.5 dB ,产生19.7dB + 11.5dB = 31.2dB的混频器定义总噪声指数。

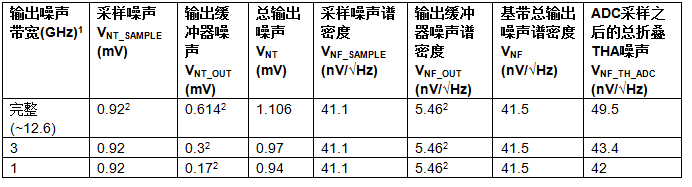

估算输出噪声频谱

为了估算输出噪声频谱,应利用如下事实:所有前端噪声都被外差或折叠到一个奈奎斯特区间中,而输出缓冲器噪声分布在输出缓冲器噪声带宽的大约7×π/2 GHz上。仿真表明,尽管小信号输出缓冲器带宽为7 GHz,HMC661LC4B和HMC760LC4B中的组合输出缓冲放大器级的有效噪声带宽约为12.6 GHz,对应于8 GHz的有效-3 dB噪声密度带宽。这种微小差异似乎是由噪声在信号链中不同带宽点的分布式贡献造成的。表1和表2显示了不同输出噪声带宽滤波情况下HMC661LC4B和HMC760LC4B的输出时域和频域噪声分量的明细,工作时钟速率为1 GHz。

获得完整输出带宽

完整输出带宽数据来自全布线寄生效应下的详细芯片仿真,但结果与实验室数据相当吻合(对于HMC661LC4B,测得的集成噪声电压VNT = 1.05 mV rms)。假定输出缓冲器噪声谱密度不变(因为滤波通常在外部进行),计算输出带宽减小的情况。表1和表2模拟了完整输出带宽情况下的VNT_SAMPLE、VNT_OUT和VNF_OUT。根据这些基本参数可直接导出所有其他量。

在采样过程中,下游ADC将输入带宽(表1和表2中所示的滤波和ADC输入带宽的组合)上的所有THA噪声外差到一个ADC奈奎斯特区间。因此,总折叠噪声是ADC噪声带宽上的总THA输出放大器时域噪声的一部分。

作为参考,使用HMC661LC4B驱动National Semiconductor ADC12D1600 ADC的数据与表1和表2中的仿真值具有很好的一致性。特别是,针对ADC快速傅立叶变换(FFT)中的谱密度,测得THA噪声分量约为37 nV/(√Hz)。National Semiconductor转换器的输入噪声带宽估计约为2.8(π/2) = 4.4 GHz。对于这种情况,总THA输出时域噪声约为0.98 mV rms,对应于43.9 nV/√Hz的噪声谱密度(经ADC采样后)。此值在ADC数字化噪声频谱中的实测THA分量的1.5 dB以内。

表1.HMC661LC4B 18 GHz带宽THA仿真和计算得到的噪声分量汇总,时钟频率为1 GHz

1、针对任何滤波和ADC带宽。

2、仿真值,所有其他值均由仿真值计算。

表2.HMC760LC4B 5.5 GHz带宽THA仿真和计算得到的噪声分量汇总,时钟频率为1 GHz

1、针对任何滤波和ADC带宽。

2、仿真值,所有其他值均由仿真值计算。

结语

为了估算THA的输出噪声谱密度,用户可以将样本时域噪声扩展到一个奈奎斯特带宽上,并在下游ADC的有效噪声检测带宽上对输出缓冲器噪声谱密度进行滤波。因此,必须获得以下估算结果:

其中:

VNT和VNT_x是时域噪声量。

VNF和VNF_x是频域谱密度。

此计算假定仅测量输出波形的保持模式部分的频谱内容。如果ADC以相同时钟速率对THA波形进行采样,则在ADC输入带宽上发生的总时域噪声(包括THA输出端的任何额外输出滤波)将扩展到一个ADC奈奎斯特区间上。原则上,这些计算可以针对任意时钟频率执行。很显然,THA采样噪声占主导地位;因此,输出滤波的影响和好处是有限的。

在较高信号频率下,时钟和信号的抖动会给采样噪声带来一个额外的噪声分量。在这种较高时钟频率下,抖动噪声不可忽略,必须包含在总噪声中。抖动噪声通常通过引用数据手册中的抖动规格进行量化,因为抖动产生的噪声很容易计算,它取决于输入频率和抖动值。一般而言,采样过程中抖动产生的噪声均方根值近似等于

VNT_JITTER ~ SR × tj

其中:

SR为采样点处的信号压摆率。

tj为均方根抖动。

对于正弦信号,压摆率(SR)峰值通过下式计算:

VIN × 2π × fSIGNAL

其中:

VIN为零到峰值信号电平。

fSIGNAL为信号频率。

经过统计平均后,用于此计算的有效压摆率基于VIN的均方根值,有效压摆率(SREFFECTIVE) = (VIN/21/2) × 2π × fSIGNAL。因此,总抖动噪声(在时域样本中)为

这种不可避免的噪声分量随着频率线性增加。因此,受抖动限制的信噪比(SNR)为

SNRJITTER ~ ?20log[1/(2π × fSIGNAL × tj)]。

要计算给定频率时的总噪声,须将抖动噪声功率与热噪声功率相加。在HMC661LC4B数据手册中,HMC661LC4B THA中的抖动值<70 fs,这是仅对THA进行专门抖动测量得到的。在THA和ADC组合测量中测得的典型值与THA单独测量的结果基本一致,约为65 fs。在给定奈奎斯特采样间隔中,这种噪声往往具有相对平坦的频谱。要通过平均降低这种噪声的电平的均值,应使用多个独立的数据记录。为了实现这种水平的子系统总抖动,必须使用良好的信号和时钟发生器并相互锁相,信号和时钟发生器的输出必须进行滤波以消除非谐波杂散信号。

即便最先进的低相位噪声合成信号发生器,也可能会给采用HMC661LC4B的采样系统带来显著的抖动,特别是当整合信号与时钟发生器之间的锁相抖动时。对施加于THA的发生器输出信号进行带通滤波,可观察发生器噪声引起的抖动的影响。在此情况下,在THA输出信号和任何经ADC FFT处理的输出频谱上可观察到对应于带通滤波器带宽的相位噪声边带。使用较小滤波器带宽以消除来自发生器的宽带噪声,可获得最佳性能。此外还必须保持合理的时钟摆率。对每个时钟差分半电路输入使用2 V/ns至4 V/ns,以实现HMC661LC4B数据手册中说明的抖动性能。如果THA用在ADC之前,则THA决定抖动,ADC的抖动基本可以忽略不计,因为它是对THA输出的稳定保持波形进行采样。还可以通过多次记录求平均或扩频处理技术来处理抖动噪声,从而提高SNR。THA抖动噪声分量同样分布在一个奈奎斯特区间内,因为它往往是宽带噪声。因此,抖动频谱噪声密度为

这三个噪声贡献(样本热噪声、样本抖动噪声和输出缓冲器噪声)不具相关性,其功率线性相加。