发布时间:2019-06-1 阅读量:1699 来源: 21ic电子网 发布人: Cloris

在PCB板子过回焊炉容易发生板弯及板翘,大家都知道,那么如何防止PCB板子过回焊炉发生板弯及板翘,下面就为大家阐述下:

1.降低温度对PCB板子应力的影响

既然「温度」是板子应力的主要来源,所以只要降低回焊炉的温度或是调慢板子在回焊炉中升温及冷却的速度,就可以大大地降低板弯及板翘的情形发生。 不过可能会有其他副作用发生,比如说焊锡短路。

2.采用高Tg的板材

Tg是玻璃转换温度,也就是材料由玻璃态转变成橡胶态的温度,Tg值越低的材料,表示其板子进入回焊炉后开始变软的速度越快,而且变成柔软橡胶态的时间也会变长,板子的变形量当然就会越严重。采用较高Tg的板材就可以增加其承受应力变形的能力,但是相对地材料的价钱也比较高。

3.增加电路板的厚度

许多电子的产品为了达到更轻薄的目的,板子的厚度已经剩下1.0mm、0.8mm,甚至做到了0.6mm的厚度,这样的厚度要保持板子在经过回焊炉不变形,真的有点强人所难,建议如果没有轻薄的要求,板子最好可以使用1.6mm的厚度,可以大大降低板弯及变形的风险。

4.减少电路板的尺寸与减少拼板的数量

既然大部分的回焊炉都采用链条来带动电路板前进,尺寸越大的电路板会因为其自身的重量,在回焊炉中凹陷变形,所以尽量把电路板的长边当成板边放在回焊炉的链条上,就可以降低电路板本身重量所造成的凹陷变形,把拼板数量降低也是基于这个理由,也就是说过炉的时候,尽量用窄边垂直过炉方向,可以达到最低的凹陷变形量。

5.使用过炉托盘治具

如果上述方法都很难作到,最后就是使用过炉托盘 (reflow carrier/template) 来降低变形量了,过炉托盘可以降低板弯板翘的原因是因为不管是热胀还是冷缩,都希望托盘可以固定住电路板等到电路板的温度低于Tg值开始重新变硬之后,还可以维持住园来的尺寸。

如果单层的托盘还无法降低电路板的变形量,就必须再加一层盖子,把电路板用上下两层托盘夹起来,这样就可以大大降低电路板过回焊炉变形的问题了。不过这过炉托盘挺贵的,而且还得加人工来置放与回收托盘。

6.改用Router替代V-Cut的分板使用

既然V-Cut会破坏电路板间拼板的结构强度,那就尽量不要使用V-Cut的分板,或是降低V-Cut的深度。

7、灌铜尽量均匀,避免灌铜与无灌铜区域热量不均衡,把板子“拉”扭曲。

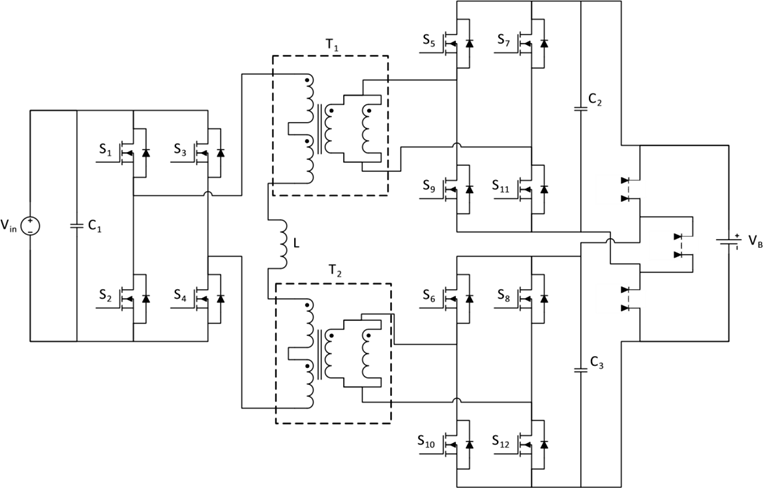

碳化硅(SiC)功率器件正以颠覆性优势引领工业充电器变革——其超快开关速度与超低损耗特性,驱动功率密度实现跨越式提升,同时解锁了传统IGBT无法企及的新型拓扑架构。面对工业应用对高效隔离式DC-DC转换的严苛需求,本文将深入解析从600W至深入解析从600W至30kW全功率段的拓扑选型策略,揭示SiC技术如何成为高功率密度设计的核心引擎。

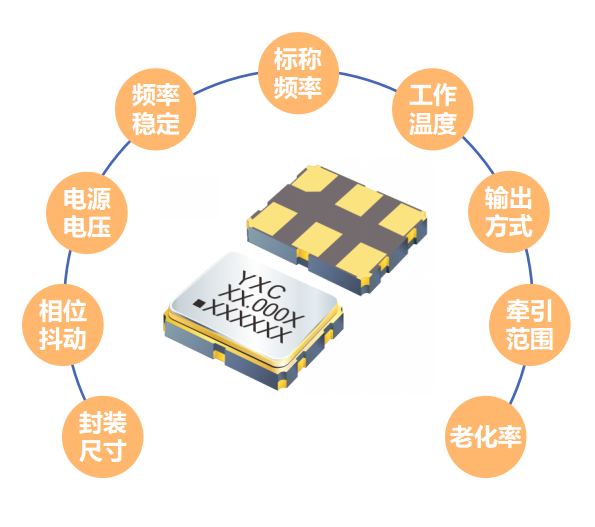

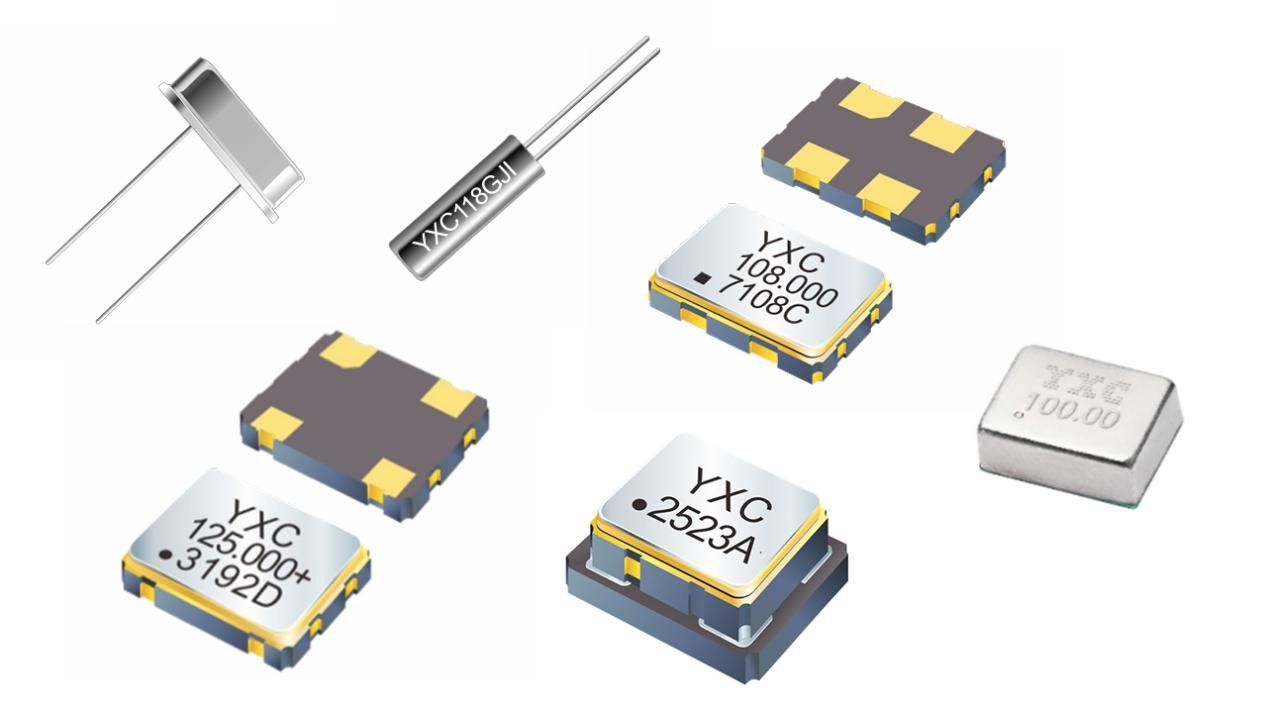

在汽车电子智能化、网联化与电动化深度融合的浪潮中,车载时钟系统的精度与可靠性正成为决定整车性能的核心命脉。作为电子架构的"精准心跳之源",车规级晶振的选型直接影响ADAS感知、实时通信、动力控制等关键功能的稳定性。面对严苛路况、极端温差及十年以上的生命周期挑战,工程师亟需兼具高稳定性与强抗干扰能力的时钟解决方案——小扬科技将聚焦车规级晶体/晶振核心参数,3分钟助您精准锁定最优型号。

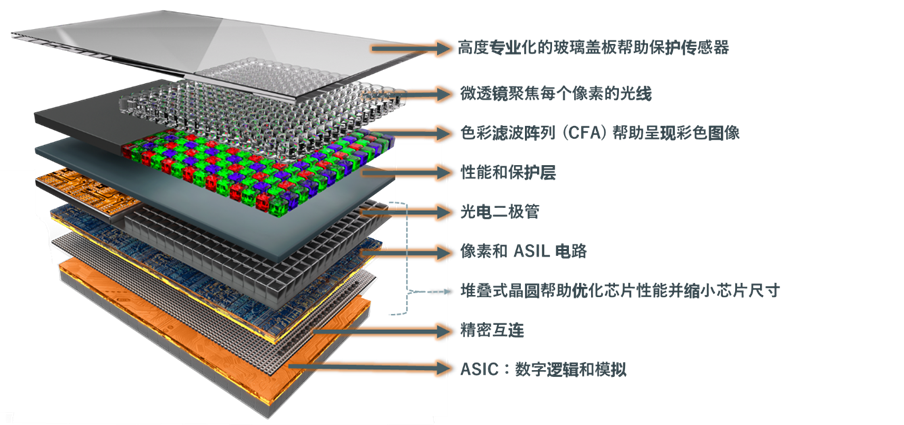

在技术创新的浪潮中,图像传感器的选型是设计与开发各类设备(涵盖专业与家庭安防系统、机器人、条码扫描仪、工厂自动化、设备检测、汽车等)过程中的关键环节。选择最适配的图像传感器需要对众多标准进行复杂的综合评估,每个标准都直接影响最终产品的性能和功能。从光学格式(Optical Format)和动态范围(Dynamic Range),到色彩滤波阵列(CFA)、像素类型、功耗及特性集成,这些考量因素多样且相互交织、错综复杂。

压控晶振(VCXO)作为频率调控的核心器件,已从基础时钟源升级为智能系统的"频率舵手"。通过变容二极管与石英晶体的精密耦合,实现电压-频率的线性转换,其相位噪声控制突破-160dBc/Hz@1kHz,抖动进入亚纳秒时代(0.15ps)。在5G-A/6G预研、224G光通信及自动驾驶多传感器同步场景中,VCXO正经历微型化(2016封装)、多协议兼容(LVDS/HCSL/CML集成)及温漂补偿算法的三重技术迭代。

在电子设备的精密计时体系中,晶体振荡器与实时时钟芯片如同时间系统的"心脏"与"大脑":晶振通过石英晶体的压电效应产生基础频率脉冲,为系统注入精准的"生命节拍";而实时时钟芯片则承担时序调度中枢的角色,将原始频率转化为可追踪的年月日时分秒,并实现闹钟、断电计时等高级功能。二者协同构建现代电子设备的"时间维度"。