发布时间:2019-12-28 阅读量:1605 来源: 我爱方案网 作者:

什么是时序逻辑电路

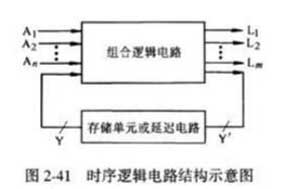

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

时序逻辑电路的设计(一)

下图的时序逻辑电路是:设计一个串行数据检测器,对它的要求是:连续输入3个或3个以上的1时输出为1,其他输入情况下输出为0。

时序逻辑电路的设计(二)

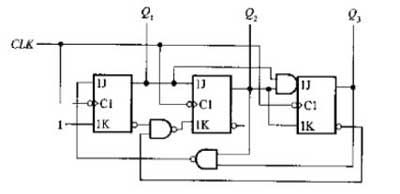

下图的时序逻辑电路是:试用JK触发器和门电路设计一个同步七进制计数器

时序逻辑电路的设计(三)

下图的时序逻辑电路是:设计一“011”序列检测器,每当输入011码时,对应最后一个1,电路输出为1

时序逻辑电路是数字逻辑电路的重要组成部分,时序逻辑电路又称时序电路,主要由存储电路和组合逻辑电路两部分组成。它和我们熟悉的其他电路不同,其在任何一个时刻的输出状态由当时的输入信号和电路原来的状态共同决定,而它的状态主要是由存储电路来记忆和表示的。同时时序逻辑电路在结构以及功能上的特殊性,相较其他种类的数字逻辑电路而言,往往具有难度大、电路复杂并且应用范围广的特点。

推荐阅读:

无源晶振与有源晶振是电子系统中两种根本性的时钟元件,其核心区别在于是否内置振荡电路。晶振结构上的本质差异,直接决定了两者在应用场景、设计复杂度和成本上的不同。

RTC(实时时钟)电路广泛采用音叉型32.768kHz晶振作为时基源,但其频率稳定性对温度变化极为敏感。温度偏离常温基准(通常为25℃)时,频率会产生显著漂移,且偏离越远漂移越大。

有源晶振作为晶振的核心类别,凭借其内部集成振荡电路的独特设计,无需依赖外部电路即可独立工作,在电子设备中扮演着关键角色。本文将系统解析有源晶振的核心参数、电路设计及引脚接法,重点阐述其频率稳定度、老化率等关键指标,并结合实际电路图与引脚定义,帮助大家全面掌握有源晶振的应用要点,避免因接线错误导致器件失效。

晶振老化是影响其长期频率稳定性的核心因素,主要表现为输出频率随时间的缓慢漂移。无论是晶体谐振器还是晶体振荡器,在生产过程中均需经过针对性的防老化处理,但二者的工艺路径与耗时存在显著差异。

在现代汽车行业中,HUD平视显示系统正日益成为驾驶员的得力助手,为驾驶员提供实时导航、车辆信息和警示等功能,使驾驶更加安全和便捷。在HUD平视显示系统中,高精度的晶振是确保系统稳定运行的关键要素。YSX321SL是一款优质的3225无源晶振,拥有多项卓越特性,使其成为HUD平视显示系统的首选。