发布时间:2022-03-23 阅读量:1438 来源: 我爱方案网整理 发布人: Aurora

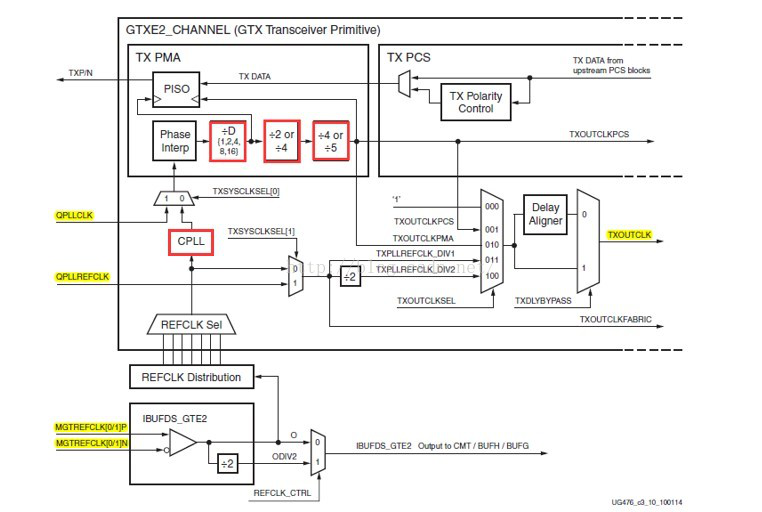

每一个收发器拥有一个独立的发送端,发送端有PMA(Physical Media Attachment,物理媒介适配层)和PCS(Physical Coding Sublayer,物理编码子层)组成,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。对于GTX的发送端来说,结构如图1所示。

图1

FPGA内部并行数据通过FPGA TX Interface进入TX发送端,然后经过PCS和PMA子层的各个功能电路处理之后,最终从TX驱动器中以高速串行数据输出,下面将介绍各个功能电路。

FPGA TX Interface(TX用户接口):TX Interface是用户数据发往GTX的接口,该接口的信号如表1所示。

表1

发送数据接口是TXDATA,采样时钟是TXUSRCLK2,在TXUSRCLK2的上升沿对TXDATA进行采样。TXUSRCLK2的速率由线速率、TX Interface接口位宽和8B/10B是否使能决定(TXUSRCLK2频率 = 线速率 / TX_DATA_WIDTH ;比如线速率是10Gb/s,TX_DATA_WHDTH等于80,那么TXUSRCLK2的频率是125MHz)。TXDATA的位宽可以配置成16/20/32/40/64/80位宽,通过TX_DATA_WIDTH 、TX_INT_DATAWIDTH、TX8B10BEN三个属性设置可以配置成不同的位宽,具体属性如表2所示。

表2

GTX的TX Interface分成内部数据位宽和FPGA接口位宽,其中内部数据归属于TXUSRCLK时钟域,FPGA接口数据归属于TXUSRCLK2时钟域,而内部数据位宽支持2byte/4byte,FPGA接口数据位宽支持2byte/4byte/8byte,因此,决定了TXUSRCLK和TXUSRCLK2有一定的时钟倍数关系,TXUSRCLK和TXUSRCLK2的时钟倍数关系如表3所示,其中TX_INT_DATAWIDTH属性设置为“0”,表示内部数据位宽为2byte,如果设置为“1”,则表示内部数据位宽为4byte(线速率大于6.6Gb/s的时候应当置“1”)。

表3

TXUSRLK和TXUSRCLK2时钟是相关联的,在时钟这两个时钟时应该遵循下面两个准则:

1. TXUSRCLK和TXUSRCLK2必须是上升沿对齐的,偏差越小越好,因此应该使用BUFGs或者BUFRs来驱动这两个时钟(因为TX Interface和PCS子层之间没有相位校正电路或者FIFO,所以需要严格对齐,本人自己的理解)。

2. 即使TXUSRCLK、TXUSRCLK2和GTX的参考时钟运行在不同的时钟频率,必须保证三者必须使用同源时钟。

发送端的时钟结构:为了能够更好的理解GTX的发送端如何工作,理解发送端的时钟结构很有必要,图2是发送端的时钟结构图。

图2

其中红框部分和黄底部分的内容是我们需要重点了解的地方,图中的MGTREFCLK是上一篇中提到的GTX的参考时钟,经过一个IBUFDS_GTE2源语之后进入GTX,用以驱动CPLL或者QPLL。对于TX PMA来说,主要实现的功能是并串转换,其并串转换的时钟可以由CPLL提供,也可以由QPLL提供,由TXSYSCLKSEL选择,TX PMA子层里面有三个红色方框部分是串行和并行时钟分频器,作用是产生并行数据的驱动时钟,其中D分频器主要用于将PLL的输出分频,以支持更低的线速率。

÷2/÷4这个选项由TX_INT_DATAWIDTH决定,如果TX_INT_DATAWIDTH为“0”,则选择÷2,反之选择÷4。

对于÷4/÷5,则由TX_DATA_WIDTH决定,如果是位宽是16/32/64,则选择÷4,如果位宽是20/40/80,则选择÷5。

对于TXUSRCLK和TXUSRCLK2由谁驱动呢,官方推荐使用TXOUTCLK驱动,这样做能精简设计,同时稳定,如何使用TXOUTCLK来做TXUSRCLK和TXUSRCLK2的驱动时钟呢,根据TXUSRCLK和TXUSRCLK2的频率关系,以一个Lane为例,图3表示TXUSRCLK=TXUSRCLK2的驱动方式,图4表示TXUSRCLK = 2*TXUSRCLK2的驱动方式。

图3

图4

对于图4,CLKOUT0的值为CLKOUT1的2倍。

TX 8B/10B Encoder:高速收发器的发送端一般都带有8b/10b编码器。目的是保证数据有足够的切换提供给时钟恢复电路,编码器还提供一种将数据对齐到字的方法,同时线路可以保持良好的直流平衡。在GTX应用中,如果发送的是D码,则需要将TXCHARISK拉低,如果是K码,则将相应的TXCHARISK拉高。

TX Buffer:了解发送的TX Buffer的作用,首先得搞清楚TX发送端的时钟域,TX发送端的时钟域如图5所示。

图5

图5中红色方框就是TX Buffer,我们都知道FIFO具有隔离时钟域的功能,在这里也不例外,我们从图中可以知道,TX Buffer连接着两个不同的时钟域XCLK和TXUSRCLK,在发送端的PCS子层内部包含两个时钟域,XCLK(PMA并行时钟域)TXUSRCLK时钟域,为了数据发送的稳定,XCLK和TXUSRCLK必须是速率匹配,相位差可以消除的,TX Buffer主要用于匹配两时钟域的速率和消除两时钟域之间的相位差。

TX Buffer也可以被旁路,TX发送端提供了一个相位对齐电路,可以解决XCLK和TXUSRCLK时钟域之间的相位差,但是TX_XCLK_SEL需设置为“TXUSR”来保持XCLK时钟域和TXUSRCLK保持同频。

TX Pattern Generator:GTX拥有伪随机数列产生电路,伪随机数列是之中看似随机,但是是有规律的周期性二进制数列,有良好的随机性和接近白噪声的相关函数,所以伪随机数列可以用来做误码率测量、时延测量、噪声发生器、通信加密和扩频通信等等领域,在GTX中可以用来测试高速串行通道传输的误码率,图6是GTX的PRBS生成电路。

图6

可以使能或者旁路这个PRBS生成电路,如果旁路的话TXDATA会传输到发送端的PMA。一般使用PRBS模式测试模型如图7所示。

图7

TX Polarity Control:TX发送端支持对TX发送的数据进行极性控制,从PCS子层输出的编码数据在进入PISO串行化之前进行极性翻转,这部分功能主要是用来弥补PCB的设计错误,如果PCB设计时不慎将TXP和TXN交叉连接的话,可以通过设置TXPOLARITY为“1”来翻转信号的极性。

晶振的启动时间,通常是指其通电后进入稳定振荡状态所需的时间。若启动时间过长,可从以下五个常见的影响因素方面进行优化。

RTC(Real-Time Clock,实时时钟)芯片作为一种独立的专用计时器件,其核心功能包括提供稳定的日历时钟、在主电源断电后持续运行、支持定时中断以及输出高精度时间戳,为各类嵌入式系统提供可靠的时间基准。

时钟系统是保障微控制器(MCU)稳定运行的核心,而晶振作为关键时钟源,主要分为无源晶振与有源晶振两种类型。下面将围绕工作原理、硬件接口、电气特性及其在MCU中的适配场景等维度,系统解析这两类晶振与MCU之间的关联逻辑。

恒温晶振(Oven Controlled Crystal Oscillator,简称OCXO)是高精度频率源的核心组件,选用切型更优(如SC切、AT切高精度型)、封装应力极小的高Q值晶片,通过恒温槽的超精密控温,让晶振始终工作在零温度系数点,几乎消除温度引发的频率漂移。

晶振倍频干扰(即高次谐波辐射)是电磁兼容(EMC)设计中非常棘手的问题,通常表现为基频25MHz的5次、7次谐波(如125MHz、175MHz等)处辐射超标。该问题源于晶振输出方波信号包含丰富的高次谐波成分,若PCB布局不当,晶振及其走线极易构成高效辐射天线,导致电磁干扰增强。