发布时间:2024-11-14 阅读量:7906 来源: 综合网络 发布人: bebop

设计高效的LC滤波器需要考虑多个因素,包括滤波器的类型、元件的选择、电路布局和实际应用需求。以下是一个详细的步骤指南,帮助你设计一个高效的LC滤波器:

LC滤波器有多种类型,包括低通滤波器、高通滤波器、带通滤波器和带阻滤波器。根据你的应用需求选择合适的滤波器类型。例如,如果你的目标是滤除高频噪声,可以选择低通滤波器。

截止频率是滤波器开始显著衰减信号的频率。你需要根据应用需求确定这个频率。例如,如果要滤除100kHz以上的噪声,可以选择100kHz作为截止频率。

滤波器的阶数决定了其滚降特性。高阶滤波器具有更快的滚降速度,但设计和实现更复杂。常见的选择是一阶和二阶滤波器。

根据滤波器类型和阶数,使用相应的公式计算电感(L)和电容(C)的值。以下是一些常用的公式:

截止频率 :

电感 和电容 :

截止频率 :

电感 和电容 ( C \):

选择高质量的电感和电容元件,以确保滤波器的性能。注意以下几点:

电感:选择低直流电阻(DCR)和高饱和电流的电感,以减少损耗和热效应。

电容:选择低ESR(等效串联电阻)和低ESL(等效串联电感)的电容,如陶瓷电容或薄膜电容。

合理的电路布局可以减少寄生参数的影响,提高滤波器的性能。注意以下几点:

短而宽的走线:减少走线的长度和宽度,以降低寄生电感和电阻。

接地设计:确保良好的接地,使用大面积的地平面,减少地线噪声。

元件位置:将电感和电容尽量靠近放置,减少引线长度。

设计完成后,需要进行测试和验证,确保滤波器的性能符合预期。可以使用示波器和信号发生器进行以下测试:

频率响应:测量滤波器在不同频率下的输出电压,验证其截止频率和滚降特性。

波纹抑制:测试滤波器对特定频率噪声的抑制效果。

假设我们需要设计一个一阶低通滤波器,截止频率为100kHz,输入电压为12V DC,输出电压要求尽可能平滑。

确定截止频率:

选择电感和电容值: 假设选择电容 :

选择元件:

电感:25.33 μH,低DCR,高饱和电流

电容:100 nF,低ESR,低ESL

电路布局:

将电感和电容靠近放置

确保良好的接地

减少走线长度

测试和验证:

使用示波器测量滤波器的频率响应

验证波纹抑制效果

通过以上步骤,你可以设计一个高效的LC滤波器,确保直流电源的输出更加稳定和平滑。

三星发布2026年财报

现场一名记者,用英语大声提出问题:“英伟达会向华为出售芯片吗? ”

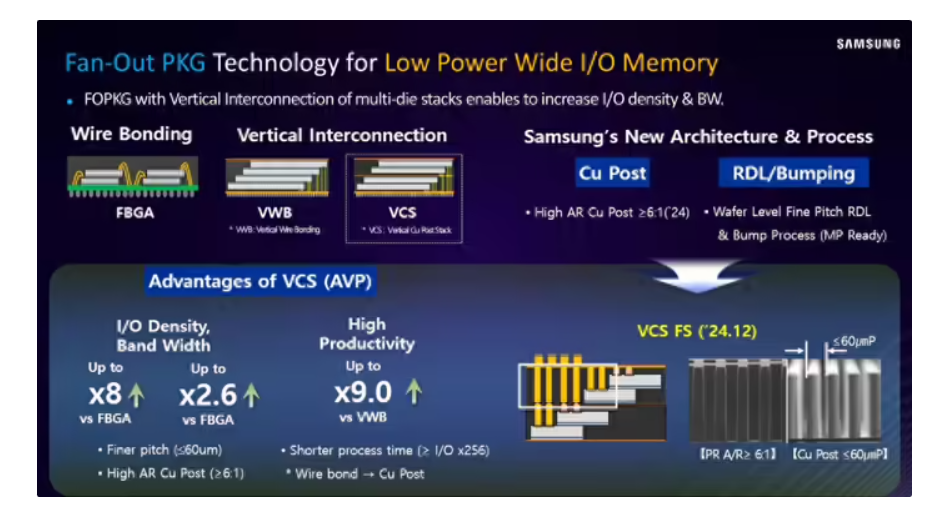

三星整研发多层堆叠FOWLP技术,以在智能手机、平板中实现更大容量、更高带宽的HBM

台积电在近期技术研讨会前发布的演示材料中披露,公司预计至2030年全球半导体市场规模将突破1.5万亿美元,较此前1万亿美元的预测值显著上调。

法院继续认定博通在与三星电子的交易中存在不当行为