发布时间:2025-02-24 阅读量:2767 来源: 综合网络 发布人: bebop

许多过程控制传感器,例如热敏电阻和应变计电桥,都需要的偏置电流。通过添加单个电流设置电阻器 R 1,您可以配置电压参考电路 IC 1 以产生恒定且的电流源(图 1 )。然而,信号源的误差取决于 R 1 和 IC 1的精度 ,并影响测量精度和分辨率。尽管您可以指定精度超过常用电压基准 IC 精度的高精度电阻,但基准电压源的误差决定了该电流源的精度。尽管制造商限度地降低了电压基准的温度敏感性和输出电压误差,但对电源变化的敏感性可能会影响其精度,特别是在必须在较宽电源电压范围内运行的过程控制应用中。

图 1 一对共源共栅连接的 JFET 可降低电源电压波动对电流源精度的影响。

一对共源共栅连接的 JFET Q 1 和 Q 2形成恒流源,限度地降低参考电路对电源电压波动的敏感度,并将 IC 1的工作电压扩展至超过其 5.5V 额定值。此外,Q 1 和Q 2 有效地将电流源的等效电阻从几兆欧增加到几乎千兆欧范围。在电路的诺顿模型中,等效电阻代表理想电流源上的并联电阻。

当栅源偏置电压为 0V 时,N 沟道 JFET 在饱和漏极电流下作为耗尽型器件运行。与需要栅极偏置电压才能导通的耗尽型 MOSFET 不同,JFET 在默认导通状态下工作,需要栅极偏置电压来切断导通。当其栅源电压相对于源极变得更负时,JFET 的漏极电流在夹断电压处变为零。 JFET 的漏极电流大致随其栅极偏压变化: I D ≈I DSS ×(1+V GS /V P ) 2,其中 I D 为漏极电流,I DSS 为饱和漏极电流,V GS 为栅极至栅极电压。 -源电压,V P 是夹断电压。

假设IC 1的输出电压V REF保持恒定在1.8V。由于输出电压驱动Q 2的栅极,因此IC 1的输入电压V IN等于V REF –V GS(Q2),即1.8V–(–1.2V)=3V。因此,Q 2的栅源电压保持在其1.2V的标称夹断电压,并且随着电流源的微小变化而同步变化。当电源电压从 3V 变化到 30V 以上时,输入电压几乎保持恒定,正如您所期望的,因为 V REF 也保持恒定。共源共栅 FET 配置使电流源的诺顿等效电阻超过了电压基准和单独的 R 1 的电阻 。您可以使用单个 JFET,但堆叠两个 JFET 可以进一步增强电路的有效阻抗。请注意,IC 1 不会降低精度,因为 JFET 使 IC 1的输入电压几乎保持恒定,并且 IC 1 有效地消除了初始栅源电压变化以及 Q 1 和 Q 2 引入的温度影响。

由V IN、V REF和V GS(Q2)组成的基尔霍夫电压环路中的负反馈允许漏极电流达到满足Q 2传输方程的 平衡偏置点。 Q 2的漏极电流由 (V REF /R 1 ) 加上 IC 1的内部“内务”电流 I GND之和组成,保持恒定。添加 Q 1可以将 Q 2输出阻抗 的影响降低到微不足道的程度。调整 R 1的值 可在 200 ?A 至 5 mA 的有用范围内改变电路的输出电流,其中 Q 2的饱和漏极电流规格规定了上限。如果您选择具有较高饱和漏极电流的 JFET,请确保不超过 Q 1的功耗。

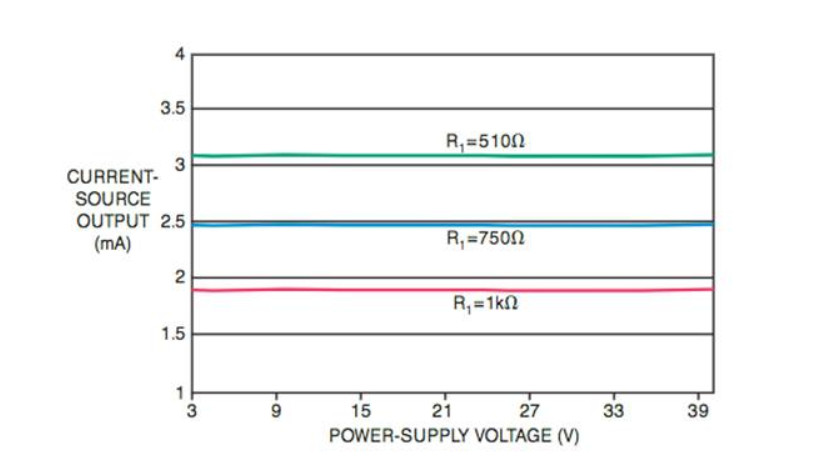

请注意,电路的电源电压下限必须超过电路的顺从电压 3V 加上传感器引入的压降:I SOURCE ×R 2。电路的电源电压上限不得超过I SOURCE ×R 2 +30V。例如,向 1kΩ 压力传感器桥 R 2提供 2.5mA 的电流,将电源电压范围限制为 5.5 至 32.5V。该电路的输出电流在很宽的电源电压范围内变化小于 1 A(图 2 )。

图 2 将 R 1设置 为 1 kΩ、750Ω 和 510Ω 的值可提供大约 1.8、2.5 和 3.6 mA 的输出电流,这些电流对宽范围的电源电压不敏感。

4月2日,兆易创新宣布正式发布新一代SPI NAND Flash产品GD5F4GM7/GD5F8GM8。

标普全球Visible Alpha研究主管Melissa Otto指出,当前推动股市创纪录上涨的人工智能巨额投资正面临显著挑战,主要由于中东危机对全球经济增长前景与能源成本带来不确定性影响。

南加州大学团队研发新型存储芯片,可在 700°C 高温下稳定运行,且未出现性能退化迹象。

联发科和高通已开始下修于晶圆代工厂的4nm投片量,显示手机链景气明显降温

EM8695 RedCap模块基于Qualcomm SDX35基频处理器,为无需传统5G全速率或复杂功能的应用提供精简型5G解决方案