发布时间:2025-07-2 阅读量:1893 来源: 安森美 发布人: wenwei

【导读】安森美SiC Combo JFET技术通过创新性集成常开型SiC JFET与低压Si MOSFET,构建出高性能共源共栅(cascode)结构,攻克了SiC器件常开特性的应用瓶颈。该方案兼具SiC材料的高压处理能力、超低导通电阻(RDS(on))与卓越热性能,以及Si MOSFET的易控常关特性,为大电流应用(如固态断路器、高功率开关系统)和多器件并联场景提供突破性的功率密度与效率解决方案。

SiC Combo JFET 技术概览

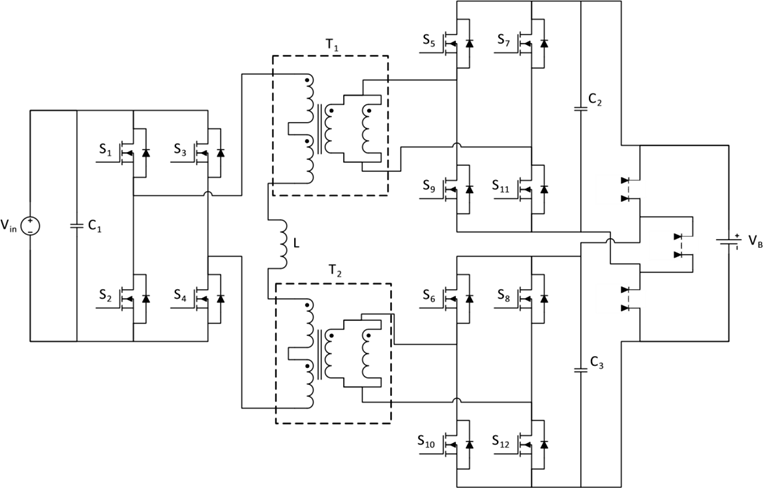

对于需要常关器件的应用,可以将低压硅(Si) MOSFET与常开碳化硅(SiC) JFET串联使用,以创建共源共栅(cascode)结构。在这种设置中,SiC JFET负责处理高电压,而Si MOSFET提供常关功能。这种组合充分利用了SiC JFET的高性能以及Si MOSFET易于控制的优点。

安森美 Combo JFET 将一个 SiC JFET 和一个低压Si MOSFET 集成到一个封装中,在满足小尺寸需求的同时,还具有高性能的常关特性。 此外,通过各种栅极驱动配置,该 Combo JFET 还提供了诸如与具有 5V 阈值的硅器件的栅极驱动兼容性、更高可靠性和简化速度控制等优势。

产品介绍

Combo JFET 将一个 SiC JFET 和一个低压Si MOSFET 集成到一个封装中,SiC JFET 和低压 MOSFET 的栅极均可使用。

图 1 Combo JFET 结构

由于 JFET 和低压 MOSFET 栅极均可使用,Combo JFET 具有多种优势。 这些优势包括过驱动(overdrive)时 RDS(on)降低,通过外部cascode 简化栅极驱动电路,通过 JFET 栅极电阻调节开关速度,以及通过测量栅极-源极压降来监测 JFET 结温。

安森美 SiC Combo JFET 产品系列

表 1 和图 2 显示了 Combo JFET产品和可用封装。

表 1 Combo JFET产品清单

图 2 Combo JFET封装和原理图

安森美 SiC Combo JFET器件的特性和优势

表 2 总结了 安森美 SiC Combo JFET器件的特性和优势

表 2 安森美 SiC Combo JFET的特性和优势

本节评估的静态特性包括 RDS(on)、峰值电流 (IDM)、RθJC(从结点到外壳的热阻)。 对于电路保护和多路并联应用,dv/dt 可控性至关重要。 以 750V 5mOhm TOLL 封装 (UG4SC075005L8S) 器件为例,评估其静态特性和动态特性。

静态特性

如表 3 所示,安森美先进的 SiC JFET 技术在市场上实现了卓越的电气性能和热性能。

表3 安森美 Combo JFET主要参数

表3 安森美 Combo JFET主要参数

安森美 Combo JFET具有低RDS(on)、高 IDM和低热阻特性。

低 RDS(on):安森美 Combo JFET器件采用 SiC JFET 技术,单位面积 RDS(on)显著降低(Rds∙A)。 该器件采用灵活、可从外部配置的cascode结构(SiC Combo-FET)来实现常关操作。在 安森美 SiC Combo JFET结构中,低电压 Si MOSFET 对总 RDS(on)的贡献不到 10%。图 1 显示了 TOLL 封装中 RDS(on)的对比。

图3 TOLL封装的RDS(on) 的对比

更高的 IDM:峰值电流对于电路保护应用至关重要,而高 IDMSiC Combo JFET正是实现这一目的的理想选择。电路保护应用因其特定的工作条件而要求稳健性和大电流穿越能力。

图4 采用 Combo JFET封装的 JFET 的 IDM

低RθJC:安森美的SiC Combo JFET采用银烧结裸片贴装技术,与大多数焊接材料相比,界面导热性能提高了六倍,从而在更小的裸片尺寸下实现相同甚至更低的结至外壳热阻(RθJC)。低RθJC有助于保持较低的结温,并确保更高的可靠性。

动态特性

通过调整 Combo JFET配置中的 JFET 栅极电阻,可实现出色的速度可控性,从而带来以下优势:

● 通过降低关断速度来减少电压过冲,可加强电路保护,尤其是短路保护。

● 易于并联,在开关损耗和动态电流平衡之间实现了出色的权衡。

功率循环

功率器件的可靠性及寿命评估对于提高系统可靠性和延长使用寿命至关重要,尤其是对于新兴的宽禁带(WBG)半导体(如SiC、GaN等)而言。功率器件的主要失效模式与热机械疲劳(TMF)有关。功率热循环测试是一种加速测试方法,被测器件(DUT)频繁地开关,使其结温以一种受控的方式循环变化。这种方法通过施加热机械应力来评估封装(接线、裸片贴装等)的可靠性。同时,它也对半导体裸片和封装元器件(接线、引线等)施加电应力,相比被动温度循环测试,能更准确地模拟实际应用中遇到的温度梯度变化。

在堆叠结构中,Si MOSFET位于SiC JFET之上,电源线连接到Si MOSFET的源极金属化层。由于硅的硬度低于碳化硅,在功率循环过程中产生的热机械应力显著减少,从而使功率循环寿命延长至原来的2倍。此外,无论是从Si MOSFET到SiC JFET,还是从SiC JFET到散热焊盘,都采用了银烧结裸片贴装(silver sinter die-attach)技术,相比现今广泛使用的焊接裸片贴装(solder die-attach,常见于SiC分立器件),进一步增强了可靠性。

栅极控制方法

用于固态断路器的 Combo JFET有两种主要控制方法:准cascode驱动模式和直接驱动模式。

图5 Combo JFET驱动模式:准cascode驱动模式(左)和直接驱动模式(右)

对于大功率开关模式应用,除了图 3 所示的上述两种控制方法外,我们还开发并推荐使用 ClampDRIVE。 或者采用最简单的栅极控制方法,用单个 JFET 栅极电阻来调整其开关速度,详见图 4。

图6 开关模式应用中 Combo JFET的控制方法(左:恒定 JFET 栅极电阻,右:ClampDRIVE)

结语

安森美SiC Combo JFET凭借革命性的低RDS(on)特性与可调开关速度,为高功率低频开关应用树立了效率与功率密度新标杆。其独特的银烧结双芯片堆叠结构,不仅实现与硅器件相当的易驱性,更将功率循环寿命提升至传统SiC MOSFET的2倍以上,为固态断路器及大电流系统提供兼具高性能与长寿命的终极解决方案。

碳化硅(SiC)功率器件正以颠覆性优势引领工业充电器变革——其超快开关速度与超低损耗特性,驱动功率密度实现跨越式提升,同时解锁了传统IGBT无法企及的新型拓扑架构。面对工业应用对高效隔离式DC-DC转换的严苛需求,本文将深入解析从600W至深入解析从600W至30kW全功率段的拓扑选型策略,揭示SiC技术如何成为高功率密度设计的核心引擎。

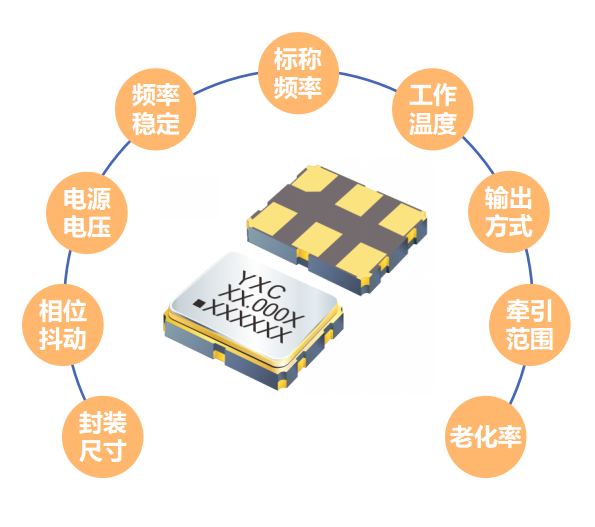

在汽车电子智能化、网联化与电动化深度融合的浪潮中,车载时钟系统的精度与可靠性正成为决定整车性能的核心命脉。作为电子架构的"精准心跳之源",车规级晶振的选型直接影响ADAS感知、实时通信、动力控制等关键功能的稳定性。面对严苛路况、极端温差及十年以上的生命周期挑战,工程师亟需兼具高稳定性与强抗干扰能力的时钟解决方案——小扬科技将聚焦车规级晶体/晶振核心参数,3分钟助您精准锁定最优型号。

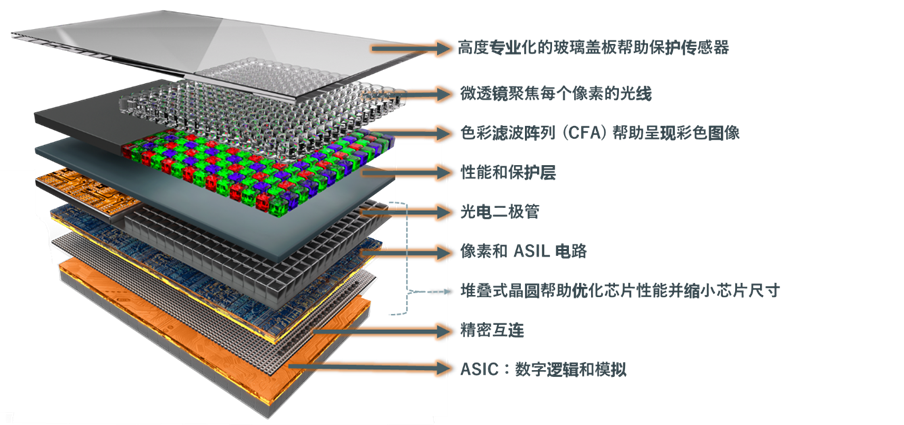

在技术创新的浪潮中,图像传感器的选型是设计与开发各类设备(涵盖专业与家庭安防系统、机器人、条码扫描仪、工厂自动化、设备检测、汽车等)过程中的关键环节。选择最适配的图像传感器需要对众多标准进行复杂的综合评估,每个标准都直接影响最终产品的性能和功能。从光学格式(Optical Format)和动态范围(Dynamic Range),到色彩滤波阵列(CFA)、像素类型、功耗及特性集成,这些考量因素多样且相互交织、错综复杂。

压控晶振(VCXO)作为频率调控的核心器件,已从基础时钟源升级为智能系统的"频率舵手"。通过变容二极管与石英晶体的精密耦合,实现电压-频率的线性转换,其相位噪声控制突破-160dBc/Hz@1kHz,抖动进入亚纳秒时代(0.15ps)。在5G-A/6G预研、224G光通信及自动驾驶多传感器同步场景中,VCXO正经历微型化(2016封装)、多协议兼容(LVDS/HCSL/CML集成)及温漂补偿算法的三重技术迭代。

在电子设备的精密计时体系中,晶体振荡器与实时时钟芯片如同时间系统的"心脏"与"大脑":晶振通过石英晶体的压电效应产生基础频率脉冲,为系统注入精准的"生命节拍";而实时时钟芯片则承担时序调度中枢的角色,将原始频率转化为可追踪的年月日时分秒,并实现闹钟、断电计时等高级功能。二者协同构建现代电子设备的"时间维度"。