一、引言

随着多媒体编码技术的发展,视频压缩标准在很多领域都得到了成功应用,如VCD(MPEG-1)、视频会议(H.263)、DVD(MPEG-2)、机顶盒(MPEG-2)等等。

而网络带宽的不断提升(ADSL接入从以前的512kbit/s提升到现在的1Mbit/s,不久还将升到2Mbit/s,甚至更高)和高效视频压缩技术的发展使得人们逐渐把关注的焦点转移到了宽带网络数字电视(IPTV)、流媒体等基于传输的业务上来。带宽的增加为流式媒体的发展铺平了道路,而高效的视频压缩标准的出台则是流媒体技术发展的关键。

H.264是ISO/IEC MPEG联合ITU-T VCEG成立的联合视频组(JVT)制定的一个全新的标准。相对于H.263+和MPEG-4(Simple Profile),H.264的码率平均降低了50%,以700kbit/s的码流速率提供了接近DVD的画面质量。

H.264能面向各种应用场合(从低比特率到高比特率),其算法本身也包含了丰富的基于压缩和网络传输的各种编码选项。可编程处理器固有的灵活性决定其为H.264的理想实现平台。众所周知,H.264的高效性是建立在其实现的高复杂度基础上的,就其Baseline而言,解码器复杂度将是H.263解码器的3倍左右,而编码器的复杂度更是高达10多倍。近年来,处理器芯片性能在不断地提高,其中包括越来越高的处理器主频,强大的运算功能以及丰富的外设。但是与当今日新月异的半导体技术、工艺相比,由于片上系统(SoC)的需求不断提高,处理器的体系结构仍具有极大的发展空间。特别是H.264作为一个前景广阔而又具有挑战性的新生“事物”,必将带动新一轮处理器架构的革新。而算法和架构的互动将会成为这一轮革新的强有力的驱动。

二、应用:处理器架构革新的驱动力

事实上,处理器架构一直是在应用的驱动下发展、进步的。

1. DSP在数字信号处理算法驱动下的产生、发展

在过去的几十年中,随着半导体工艺与集成电路设计技术的逐渐发展,微处理器逐渐在工业控制等领域得到应用,简单的智能控制与少量计算任务的实现,都是由我们通常所谓的单片机来完成的。单片机虽然集成了CPU、RAM、ROM(EPROM或EEPROM)、时钟、定时/计数器、多种功能的串行和并行I/O口等部件,但是其面向的应用场合主要是工业控制中各种事件的管理调度等,运算处理能力不足一直是它的缺陷。

特别是随着信息化的进程和信号处理理论与算法等的迅速发展,需要处理的数据量越来越大,对实时性和精度的要求越来越高,单片机越来越难以满足不断上升的要求,DSP应运而生。

DSP的产生背景决定了其架构的重点更多的是对特定的数字信号处理算法的强化支持。典型的数字信号处理算法,例如在有限长冲击响应滤波器(FIR)的实现中,需要在系数和输入样本的滑动窗口间作乘法,然后将所有的乘积进行累加。类似的运算在数字信号处理过程中大量地重复发生,使得为此设计的器件必须提供专门的支持。通常DSP处理器使用专门的硬件来实现单周期乘法,并且还增加了特殊的累加器寄存器来处理多个乘积的和。为了充分体现专门的乘法累加硬件的好处,几乎所有的DSP的指令集都包含有显式的MAC指令。另外,为了提高特定算法的实现效率,一些DSP处理器有专门的硬件来实现特殊的寻址模式,例如,模块(循环)寻址(对实现数字滤波器延时线很有用)、位倒序寻址(对FFT很有用)。这些特殊的寻址模式如果用软件来实现,则会大大降低系统的性能。

为了提高每个指令周期内数据(与指令)的吞吐量,大多数DSP采用了改进的哈佛结构,并且使用了多个片内存储器和多组总线。此外,DSP处理器几乎都不具备数据高速缓存,这是因为DSP的典型数据是数据流。也就是说,DSP处理器对每个数据样本做计算后就丢弃了,几乎不再重复使用。另外,DSP算法中,通常大多数的处理时间是在执行较小的循环上,因此,大多数DSP设有专门的硬件用于零开销循环。所谓零开销循环是指处理器在执行循环时,不需要进行循环计数器的检查、条件跳转以及修改计数器值等操作,从而大大增强了DSP的性能。

这些结构上的改进极大地提高了DSP在运算密集型应用中的处理能力。但随着新的算法与标准的不断出现,对处理器运算能力的要求仍在不断提高。为了达到实际应用的需要,处理器的架构仍然在不断的发展中。

2. 超标量、VLIW处理器架构

高性能DSP在应用中取得了巨大成功,其成功的基础在于半导体工艺的不断进步使其性能不断提高,从而使其应用领域越来越广泛。但其在市场上真正的活力却是其可编程特性。只要到自己购买商品的厂商网站下载更新软件就能“免费”升级消费品,还有什么事情比这更让消费者满意呢?有了消费者的支持,企业当然能长盛不衰。

因此,人们从来没有停止过更高性能处理器的架构研究。这其中就有多发射的超标量结构(Superscalar)和将若干指令组合在一起的超长指令字结构(VLIW),共同之处都是为了开发指令级并行性(ILP,Instruction Level Parallel)。从提高处理器性能的出发点来看,其思想的先进性不容置疑。但在2004年的消费电子领域,呼声更高的似乎是另一种架构:RISC(MCU)/DSP架构。典型的是ADI的Blackfin系列处理器,其重要特色就是在结构中充分体现对媒体应用(特别是视频)算法的支持,另外在售价、功耗方面也具有很大优势。笔者认为,这些正是超标量与VLIW架构的处理器所欠缺的。

三、H.264:新一轮媒体处理器架构革新

目前,结合视频处理算法,多项有效技术被采用。

1. SIMD技术:数据可并行处理特性

为提高通用DSP的媒体处理能力,各大DSP厂商都在原有架构基础上进行了媒体处理指令集扩展。其中,SIMD是被人们所熟知,也是最为成功的一项技术(图1)。现已几乎被所有面向媒体处理相关领域的处理器所采用。SIMD技术通常通过内核中内置多个运算单元以及相应的控制、数据通路来实现,反映给用户的是提供了支持SIMD操作的指令集。

SIMD技术利用了视频算法:DCT/IDCT,ME/MC(运动估计、运动补偿)等算法模块中的可并行特性。

2. 数据预取技术:数据准备、运算写回并行操作

在这里,我们把数据处理分如下三个步骤:(1)数据准备;(2)数据处理;(3)数据写回。

事实上,在视频处理中,(1)和(3)有两层含义。第一层指的是片内、片外的数据读写操作。理想情况是尽量减少数据读写的时间(往往把这部分看成是额外开销)。从实践上看,可以通过DMA机制实现DSP数据处理和片内外数据调度的并行处理。第二层指如何取得SIMD处理中的各个子数据,例如图中(X3,X2,X1,X0)和(Y3,Y2,Y1,Y0)的获取以及操作(具体随OP不同而异)的并行处理。实际上,DSP(区别于单片机与RISC)中基于存储器的寻址方式就是一种节省数据存储器访问时间的有效技术。真正意义上的指令中操作数装载和并行运算的功能在Blackfin系列处理器中有了很好的体现。

而上述两层含义的思想却是相同的,那就是数据处理和数据存取的并行处理(图2):处理当前数据的同时,把下次处理的数据预取(读)进来或把上次计算结果写回存储器。

视频处理是一个以数据处理为主的系统,结合视频处理算法,实现指令操作数装载和并行运算将大大提高数据处理效率。

3. 基于可编程处理器的H.264实现策略

H.264在复杂度上大大高于以往标准,这就要求处理器在架构上必须找到新的突破。笔者认为,以下两点将是基于可编程处理器的H.264算法实现的有效手段。

(1)针对H.264具体算法实现进一步进行指令扩展。

在H.264中由于增加了很多以往标准所有没有的编码技术,例如整数变换(结合量化),去方块效应滤波器,以及精度更高的运动估计和补偿等等,这就要求在指令集上必须进行扩展。

值得一提的是,在H.264中运动估计采用了多帧参考技术,这要求处理器设计人员对处理器的数据调度机制以及片内外存储器的组织等必须有新的考虑。

(2)双核、多核架构适配H.264编码器的可并行处理特性。

在H.264当中,和以往标准一样可以进行基于图(picture)、片(slice)和宏块级的并行处理。而且,在H.264中采用RD算法进行模式选择,所有的模式在计算时都不存在相关性,即可以并行操作。因此,双核、多核架构在单核处理能力不够的情况下,也将被人们接受。随之而来的是软件工作难度(如编译器,操作系统任务调度等)将会大大增加。

针对以上两点,值得一提的是ADI 的Blackfin系列处理器。该系列处理器中BF531/533/535均为单核架构,均进行SIMD指令集的扩展。而其中的并行指令(运算类指令和存储器操作指令可以并行执行)有力地提高了数据处理为主的视频编解码器系统的性能。目前该款处理器正向多核架构发展(如基于双核的BF561)以适应H.264如此高复杂度的算法的实现,这将是未来几年内提升处理器性能的一个有效途径,也将为高复杂度的H.264的实现奠定基础。而Blackfin系列处理器在功耗、成本等方面的指标也是其受到人们关注的一个原因。

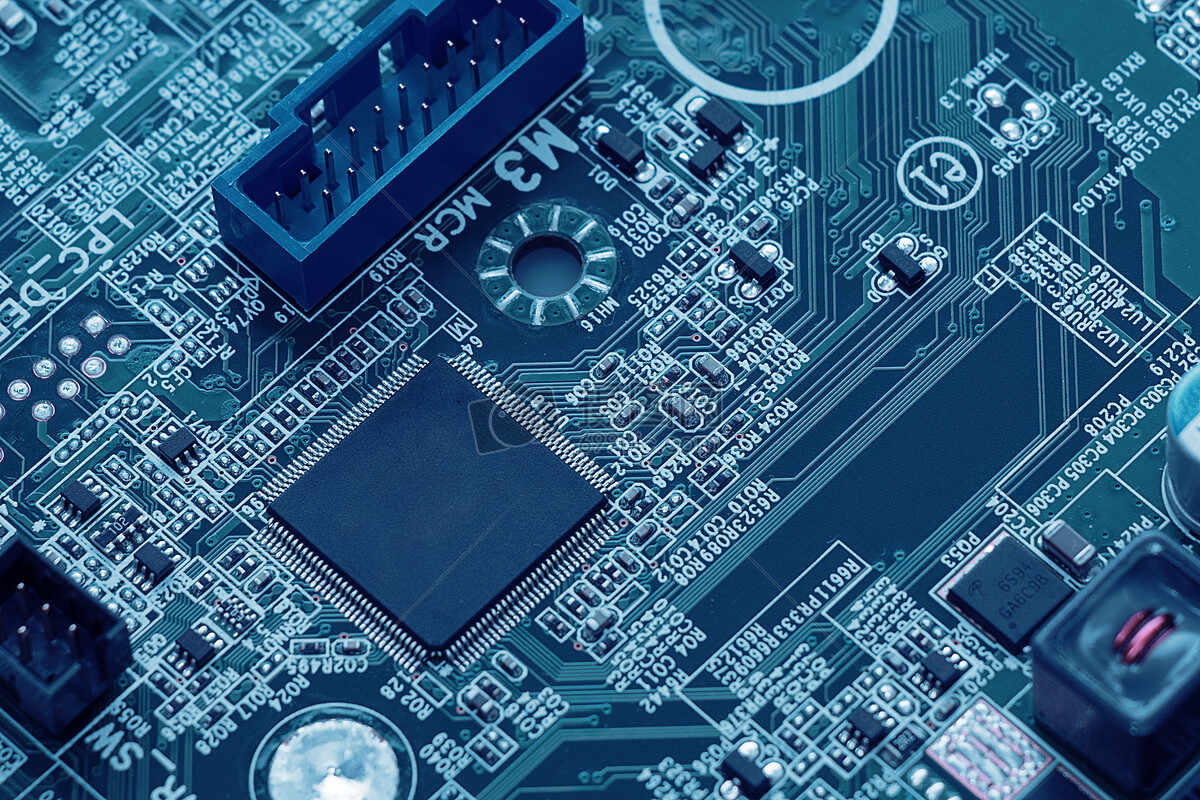

四、MediaSOC3201A:一种非对称结构的双核系统芯片

浙江大学信息与通信工程研究所SoC R&D小组自2004年4月研发成功国内首款具有自主知识产权的RISC/DSP混合体系结构处理器MediaDSP3200以来,于2004年底成功研制出基于双核的音视频SOC样片(MediaSOC3201A),如图3,其样片如图4。区别于BF561的对称架构(SMP),MediaSOC3201A是一种非对称结构(AMP),主要包括:媒体扩展CPU(运行操作系统,承担音频解码、系统控制以及部分视频解码任务),多功能处理器MediaDSP3201(数字信号处理、媒体处理指令扩展处理器:浙大数芯,负责视频处理等数据处理任务),多任务DMA(负责数据调度),各种同步、异步存储控制器,视频编码器(支持NTSC、PAL等制式),IIS音频播放以及GPIO等外设接口。

目前,课题组正在研究基于MedisSOC3201A的H.264算法实现。算法、架构协同考虑是我们的目标。课题负责人刘鹏教授正满怀信心地带领整个研发团队为中国的集成电路、媒体系统芯片事业添砖加瓦。