发布时间:2010-11-25 阅读量:2305 来源: 发布人:

模拟视频信号解码由TVP5146芯片组成,该部分主要完成PAL-D制式模拟视频信号解码,输出符合ITU-RBT656[5]且内嵌同步字符4:2:2格式数据供FPGA采集。TVP5146支持NTSC、PAL、SCEAM、CVBS、S-video制式视频输入,具有RGB转换为YCbCr功能。

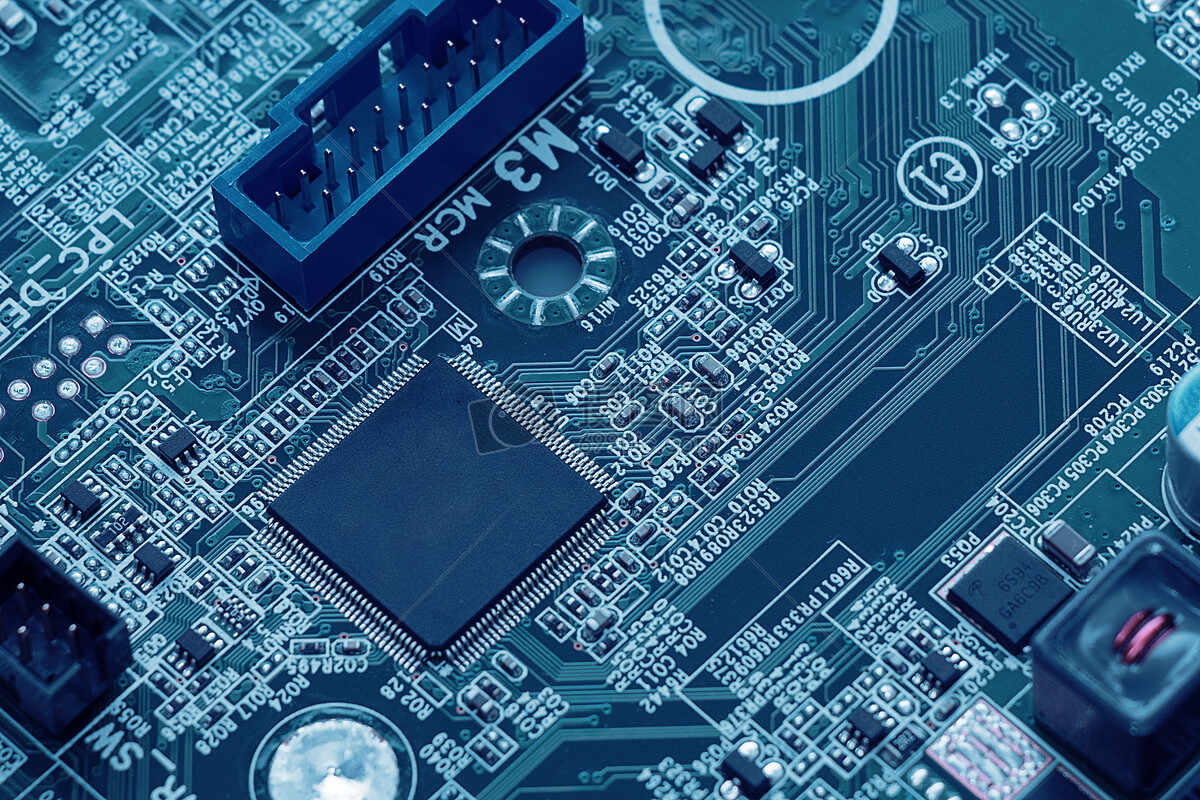

视频数据采集部分由FPGA控制芯片、SSRAM、Flash、电源芯片、辅助外围电路组成。该部分以TVP5146输出像素时钟作为FPGA采集时钟采集解码后的数据,在系统时钟的控制下,交织乒乓存储于SSRAM芯片,并在帧信号控制下交换存储体。FPGA采用Altera公司CycloneII系列EP2C35F672[6]芯片,该芯片具有33 216个逻辑单元,内部RAM高达484 KB,支持NiosII嵌入式处理器,核心电压1.2 V,IO电压3.3 V,具有4个PLL输入,12个PLL输出。Altera的FPGA采用SRAM工艺,掉电就会丢失配置数据,所以外部需要挂接存储配置数据的部件。Altera公司FPGA一般都支持串行被动配置、串行主动配置、JTAG配置,通过跳线选择配置方式,JTAG配置在调试时很方便。串行主动配置一般需要Altera公司的专用配置芯片,在系统上电后主动配置芯片。FPGA配置完成后,NiosII从Flash中读取程序,完成相应的功能。TVP5146采用I2C口配置其工作方式,配置的数据亦存储在Flash芯片中。SSRAM采用CY7C1380D,32 bit数据位宽,2 MB存储空间,3.3 V供电,提供高性能3-1-1-1访问时钟周期速率,最高频率达250 MHz。

图像处理在FPGA片内实现,进行YCbCr转RGB、RGB转灰度、线性插值等处理,DVI编码显示在DVI接收芯片Si178片内完成,在系统时钟的控制下,依照DVI显示时序,控制行、场同步信号,依次把RGB像素送入编码芯片,完成图像数据的编码和传输。Si178具有25~165 M点像素每秒,24 bit模式,I2C编程接口,支持热插拔,兼容DVI1.0标准,3.3 V供电。

2 模拟视频信号解码

视频解码格式有ITU-RBT.601标准格式和ITU-RBT.656标准格式。ITU-RBT.601标准需要行、场同步信号线,ITU-RBT.656标准无需同步信号线。ITU-RBT.656标准采用8 bit传输格式,亮度信号Y和色度信号Cb/Cr交替传输。本设计采用ITU-RBT.656标准。我国电视制式为PAL-D,一帧电视图像有625行,每行可视像素为720个,因为有行消隐和场消隐,实际可视像素面为720×576,电视图像传输采用奇偶场交替传输,所以通常奇偶场各传输288行。图2是行同步4:2:2输出时序图。

PAL-D制式一行可视像素有720个,因为采用ITU-RBT.656标准,每2个DATACLK时钟才输出一个像素,所以,一行可视像素需要1 440个DATACLK时钟。一行像素输出完毕后紧接4个行结束标志,然后进入行消隐阶段,行消隐阶段结束后,4个字符的开始标志表明一行的开始,从4个结束标志到4个开始标志,共有288个DATACLK时钟。这288个DATACLK期间的数据不用于显示,用于同步和消隐,所以对于PAL-D制式,采用ITU-RBT.656标准传输一行视频需要1 728个DATACLK时钟[7]。

EAV和SAV分别表示一行有效视频的结束和开始,EAV/SAV序列由FF-00-00-XX表示,其中XX是状态字,表1为EAV/SAV序列字段位表。

F场标志:F=0是偶场,F=1是奇场;V视频有无效标志:V=0为有效视频数据,V=1为无效视频数据;H有效视频结束起始标志:H=0是SAV,H=1是EAV。

从624行~22行和311行~335行为无效视频行,此时V=1;从23行~310行和336行~623行为有效视频行,此时V=0。从1行~312行为偶场,此时F=0;从313行~625行为奇场,此时F=1。

配置TVP5146使其正确初始化。设置正常工作模式,视频选择输入口,色度和亮度AGC自动增益,视频输入为PAL-D制式625行,解码输出格式为10 bit 4:2:2(2倍像素时钟速率)内嵌同步字符,实际10 bit输出时最低2 bit可丢弃。设置亮度信号范围为16~235,色度信号范围为16~240。配置NiosII软核,设置CPU类型为经济型32 bit,CPU时钟频率为100 MHz,复位向量起始地址为Flash,异常向量起始地址为On-chip-ram,设置PIO线模拟I2C协议,用于配置TVP5146,配置Avalon-MM三态桥用于挂接Flash,配置On-chip-ram为32 KB[8],添加一个Avalon从设备。该从设备为用户自定义接口,NiosII软核可以通过该从设备口实时访问转换后的RGB像素,进行图像处理。

3 视频图像数据采集

视频解码芯片输出内嵌同步字符8 bit视频数据,参照解码芯片输出DATACLK时钟,FPGA采集视频解码数据。FPGA采集之前先要进行图像裁剪、交织处理。裁剪处理是为了产生640×480的像素面,交织处理即变隔行视频数据为逐行视频输出,即两场图像交叉嵌入一个存储体中,形成一帧。当一帧存储完毕后,切换存储体,而先前的存储体内容参照系统时钟,依次像素处理送DVI编码芯片进行显示。

3.1 视频信号采集控制

视频输出信号为内嵌同步字符8 bit Y:Cb:Cr=4:2:2输出,本设计中视频信号采集采用状态机控制法。视频信号采集控制状态机表示如图3所示。

Idel:默认空闲状态。如果视频采集标志capture置位,则进入Wait State状态;如果capture不置位,则停留在Idel状态。

Wait State:此时如果收到数据0xff,则进入State1,其他情况仍然循环停留。

State1:如果此时收到数据0x00,则进入State2;收到其他数据则进入Error。

State2:如果此时收到数据0x00,则进入New page状态,否则状态返回到Wait State。

New page:此时视频处于消隐状态,如果收到的视频数据vpo[6:5]=01,则正在消隐,转入第一行数据接收状态First Line,否则跳回Wait State状态。

First Line:如果收到vpo[6:4]=000,表明下一个数据即视频图像数据,否则返回到Wait State。

Chroma blue:正确有效的数据,如果此时接收到vpo=0xff,则表明数据转入End Line,如果收到vpo=0x00,则转入Error状态。

Luma blue:亮度蓝色数据,接收完转入Chroma red状态。

Chroma red:色度红色数据,接收完转入Luma red状态。

Luma red:亮度红色数据,接收完转入Chroma blue状态。

End Line:如果vpo[6:4]=011,表示奇数场结束,偶数场将要开始,转入New line状态;如果vpo[6:4]=111,表示一帧数据结束,转入Idle状态;如果vpo[5:4]=01,表示一行结束,下一行将要开始,转入New line状态;否则进入Error状态。

New Line:如果接收到的vpo[5:4]=00,表示有效数据接收,转入Chroma blue状态;否则转到End Line状态。

Error:错误状态,ITU-RBT656规定Y=[16 235] CBCR=[16 240]范围内,越此范围就为错误状态。如果capture=1,跳转到Wait state状态,否则停留在Error状态。该系统具有自动错误恢复能力。

3.2 图像剪裁处理

PAL-D制式视频在ITU-RBT.656标准下,输出像素面为720×576大小,而本设计中要求输出大小为640×480像素面,所以必须使得行720像素变为640个,采用每9个像素丢弃1个像素,因为Y/Cb/Cr是交替输出的,即Cb-Y-Cr-Y传输,每个像素都有亮度数据Y,但是色度Cr和Cb是交替的。如果第1个像素是Cb和Y数据,则第8个像素即为Cr和Y数据,第9个像素为Cb和Y数据,现在丢弃第9个像素数据,先把第10个素的Cr数据和第11个像素的Cb交换,这样就保持了Cb和Cr的交替。视频中采取每6行可视像素丢弃1行,对于576行可视像素,实际丢弃96行,即变为实际可显示480行。

3.3 图像交织与存储处理

视频信号采集控制处理后产生行、场、帧、视频有效标志及每场视频行数、每行像素点数。本设计利用这些信号组合作为存储地址控制字写入SSRAM,每2个DATACLK为1个像素数据,4个DATACLK为2个像素数据32 bit,FPGA控制每4个DATACLK写入一次32 bit数据。

每场视频可视行为288行,占用2进制位9 bit,奇偶场标志1 bit,每行像素有640个,存入SSRAM时按照每2个像素写入一次,故每行像素为360个写入次,设计为9 bit,总共为19 bit,正好占用完19 bit地址线。

奇偶场标志就是上述EAV/SAV状态字中的F,电视视频中,首先传输的是偶数场,此时A9=0;其次传输的是奇数场,此时A9=1。帧控制位frame定义为1 bit,当完成一帧的传输后就使frame<=frame+1,这样帧控制位就是0-1-0-1-0-1序列,完成一帧传输就翻转一次。帧控制位用来切换存储体,当帧控制位切换在第一片SSRAM上时,偶数场先存入到SSRAM中,然后奇数场数据嵌入到SSRAM中。

4 图像处理和DVI编码显示

视频采集的图像已经交替存入SSRAM中,当一帧存储完毕,该存储体就可以进行处理上传。图像处理包括Y/Cb/Cr 4:2:2格式转化为Y/Cb/Cr 4:4:4,Y/Cb/Cr转化为RGB格式,可实时RGB像素处理,像素处理后按照行、场同步信号依次送入DVI芯片。

4.1 YCrCb转RGB处理

首先处理的是Y/Cb/Cr 4:2:2格式转化为Y/Cb/Cr 4:4:4格式,就是对每个像素扩展其色度数据,使得每个像素为24 bit。其中8 bit为亮度数据,8 bit为Cr数据,8 bit为Cb数据。

由YCrCb数据转换为RGB数据可按照下式:

R=1.164×(Y-16)+1.596×(Cr-128)

G=1.164×(Y-16)-0.813×(Cr-128)-0.392×(Cb-128)(1)

B=1.164×(Y-16)+2.017×(Cb-128)

实际上FPGA片内不能进行小数运算,因此把需要运算的数左移9 bit,且运用FPGA片内的乘法器宏单元完成。则式(1)变为式(2):

R=596×Y+817×Cr-114 131

G=596×Y-416×Cr-200×Cb+69 370(2)

B=596×Y+1 033×Cb-141 787

这样得到的RGB信号只需要右移9 bit就可以得到正确的8 bit数据位宽度的RGB信号,对RGB像素的处理受NiosII核控制,挂接在NiosII核上的Avalon从设备有3 bit控制信号,其值从0~7,分别对应灰度处理、像素水平线性放大插值处理、水平缩小处理、原三彩色输出和无定义。

若进行灰度处理,则按照下式计算:

Y=0.299×R+0.587×G+0.114×B(3)

在计算时也需要先左移9 bit,采用3路乘法MULT_

ADD宏单元计算,计算结果右移9 bit。如果进行水平像素放大,则采取线性插值法,其他图像处理按照相应算法进行。

4.2 视频数据输出和DVI配置

DVI输出刷新频率为75 Hz,输出屏幕像素为640×480,查VGA时序表得到在640×480@75 Hz时,水平像素总共为840,垂直像素总共为500,行频为37.5 kHz,点时钟频率为31.5 MHz,这个频率由FPGA片内PLL倍频得到。配置DVI芯片引脚,设置IDCK+为像素时钟31.5 MHz,IDCK-接地,DE表示有效像素数据使能,其值在有效行和有效列内为高电平,否则为低电平。行、场同步信号由在FPGA片内编写的DVI模块产生时序控制。通过I2C口配置SiI178芯片,设置其为正常工作方式,VSYNC、HSYNC为正常输入状态,输入总线为24 bit宽,IDCK+下降沿将数据打入DVI编码芯片。

系统采用FPGA为主控芯片,通过一片FPGA完成视频解码数据的采集和图像处理,并在FPGA片内配置NiosII软核,作为初始化TVP5146和SiI178使用,在图像处理模块中挂接Avalon从设备,YCbCr转换为RGB后可以通过NiosII处理器编写C算法处理或者通过NiosII的标志信号进行处理,处理结果直接送DVI编码器。采用乒乓交织算法,保证了图像不闪烁和无锯齿现象。

三星开启内部审查,严查员工收受不当回扣行为

长江存储正逐渐成为消费电子领域(包括PC与智能手机)为数不多的稳定供应来源。

据苏州高新区发布消息,12月18日,维谛技术华东研发制造基地战略合作项目签约仪式在苏州高新区举行。

由于半导体短缺,日本汽车大厂本田宣布实施短期停产与减产措施

近日,工业和信息化部部长李乐成在北京会见美国超威半导体公司(AMD)董事会主席兼首席执行官苏姿丰。