发布时间:2025-03-26 阅读量:1535 来源: 我爱方案网 作者: 杨兴科技

【导读】随着PCIe 5.0技术在高性能计算、数据中心及AI应用中的普及,其单通道32 GT/s的超高速率对参考时钟性能提出了前所未有的挑战。PCIe 6.0虽进一步将速率提升至64 GT/s并引入PAM4调制技术,但其底层稳定性仍依赖于高精度时钟信号的同步与纠错能力。在此背景下,YXC推出的HCSL输出差分晶振(如YSO230LR/YSO231LJ系列)以超低相位抖动(0.05ps RMS)、±25ppm全温区频差精度及2.5×2.0mm微型封装,成为PCIe 5.0参考时钟设计的核心解决方案,精准解决高速信号同步、多设备协同及噪声抑制等关键技术瓶颈,助力新一代硬件突破性能边界。

一、PCIe协议与参考时钟要求

1、PCIe是什么?

PCI Express(Peripheral Component Interconnect Express)是一种高性能、高带宽的串行总线标准,用于连接计算机内部的各种硬件设备,如显卡、存储设备(SSD)、网卡等。它取代了传统的 PCI 和 AGP 总线,并以其高速度、低延迟和强扩展性成为现代计算机系统的核心互联技术。

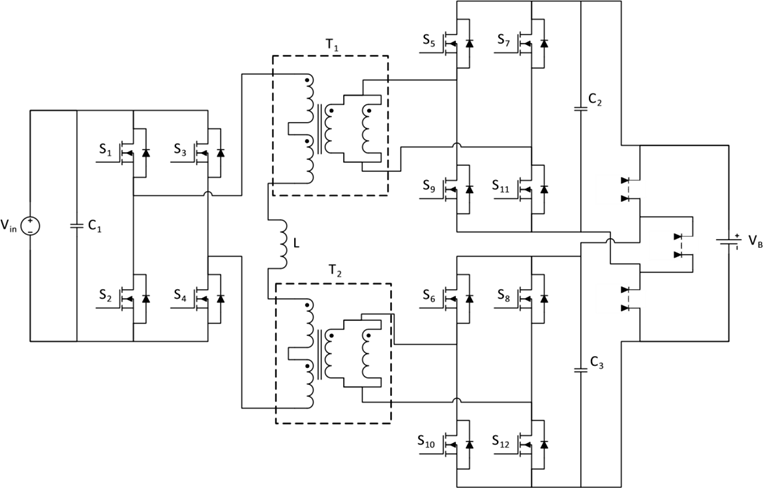

PCIe 支持多种速率版本,包括 PCIe 1.0、PCIe 2.0、PCIe 3.0、PCIe 4.0、PCIe 5.0和PCIe 6.0,每个版本都在前一代的基础上实现了带宽的翻倍。

PCIe 6.0已于2022年发布,其单通道速率提升至64 GT/s,并引入PAM4调制技术,带宽再次翻倍。同时,PCIe 6.0还增加了FEC(前向纠错)功能,以应对高速传输中的信号衰减问题。

图1:PCIE 6.0协议标准

2、PCIe参考时钟的关键作用

在PCIe系统中,参考时钟(Reference Clock)是确保数据传输准确性和稳定性的核心组件。其主要作用包括:

● 同步数据传输:为SerDes(串行器/解串器)提供精准时钟信号,确保发送端与接收端同步。

● 降低误码率:高精度时钟减少信号抖动,降低数据传输误码率(BER)。

● 支持多设备协同:在CXL、NVMe-oF等复杂架构中,参考时钟需实现多设备间的相位对齐。

PCIE协议下的参考时钟基本为100MHz HCSL输出,要求确保数据传输的正确性和稳定性,解决时钟抖动、偏移和噪声问题。

随着PCIe版本的升级,参考时钟的性能要求也大幅提高,下表展示了不同PCIe协议版本对于参考时钟RMS抖动的要求:

表1:不同PCIe协议版本对于参考时钟RMS抖动的要求

二、HCSL输出差分晶振:满足PCIe 5.0时钟需求的理想选择

为应对PCIe 5.0对参考时钟的严苛要求,推荐使用差分振荡器YSO230LR系列和YSO231LJ系列。这两款产品凭借卓越的性能和可靠性,成为PCIe 5.0参考时钟的理想选择。

产品优势:

● 超低抖动:相位抖动可达0.05ps(typ.) RMS,满足PCIe 5.0的严苛要求,确保信号完整性;

● 高稳定度:总频差最优可达±25ppm @ -40~﹢85℃;

● 差分输出:支持HSCL、LVDS、LVPECL等多种差分输出;

● 小型化:提供2.5*2.0mm紧凑设计,适配高密度主板布局;

● 宽温范围:提供-40℃~﹢105℃、-40℃~﹢125℃等宽广的工作温度选项。

推荐阅读:

iPhone 18芯片性能飞跃!台积电2nm工艺曝光:速度提升15%、能效暴涨30%

DRAM市场迎转折点:HBM量产带动价格止跌,多领域需求回暖支撑二季度行情

印度PC与平板市场2024年创2000万台新高 企业采购与消费升级驱动未来增长

TDK推出车载大电流PoC电感器ADL3225VF:1600mA驱动能力助力ADAS布线革新

碳化硅(SiC)功率器件正以颠覆性优势引领工业充电器变革——其超快开关速度与超低损耗特性,驱动功率密度实现跨越式提升,同时解锁了传统IGBT无法企及的新型拓扑架构。面对工业应用对高效隔离式DC-DC转换的严苛需求,本文将深入解析从600W至深入解析从600W至30kW全功率段的拓扑选型策略,揭示SiC技术如何成为高功率密度设计的核心引擎。

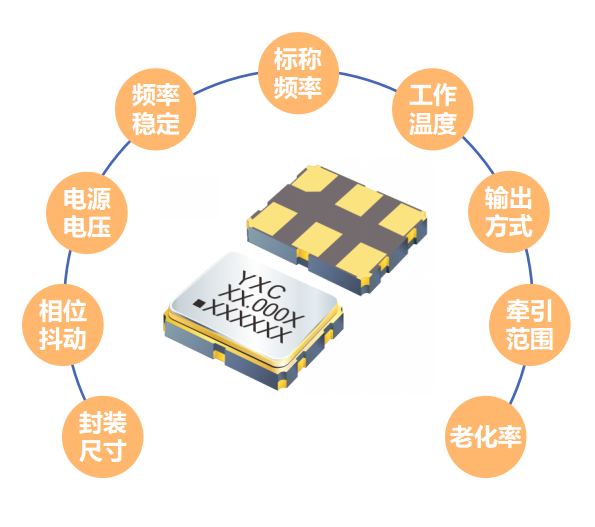

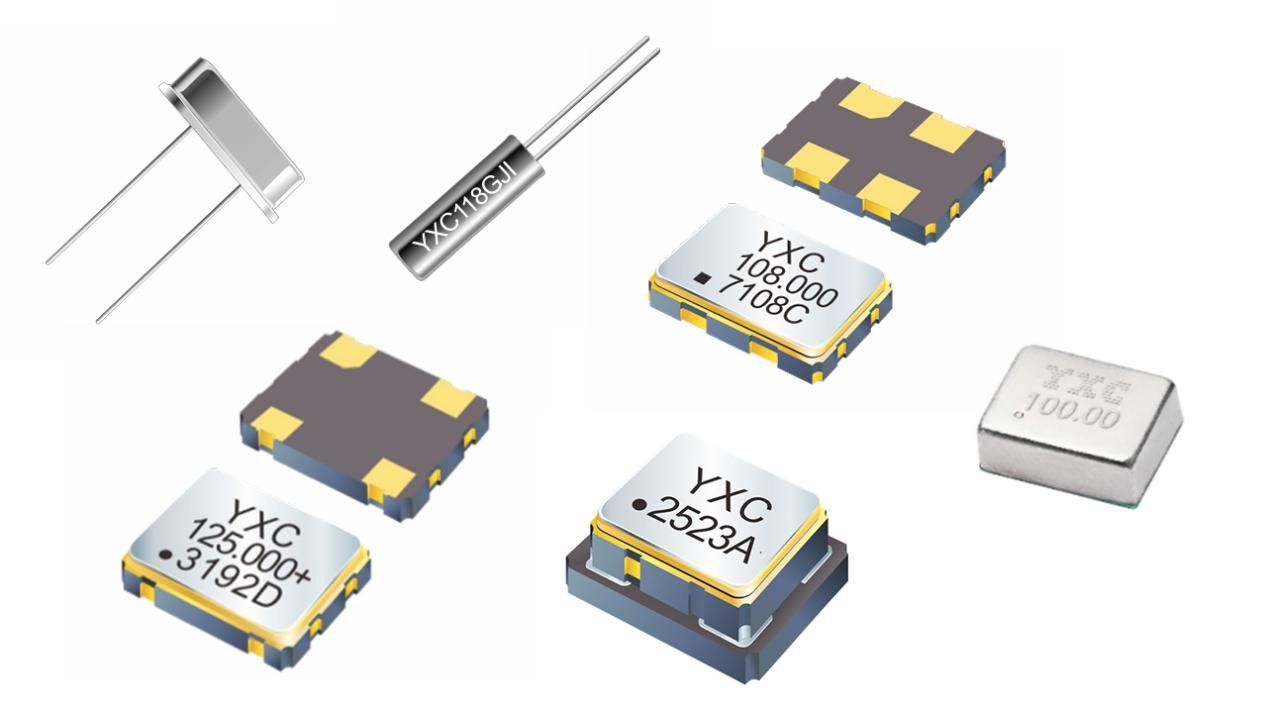

在汽车电子智能化、网联化与电动化深度融合的浪潮中,车载时钟系统的精度与可靠性正成为决定整车性能的核心命脉。作为电子架构的"精准心跳之源",车规级晶振的选型直接影响ADAS感知、实时通信、动力控制等关键功能的稳定性。面对严苛路况、极端温差及十年以上的生命周期挑战,工程师亟需兼具高稳定性与强抗干扰能力的时钟解决方案——小扬科技将聚焦车规级晶体/晶振核心参数,3分钟助您精准锁定最优型号。

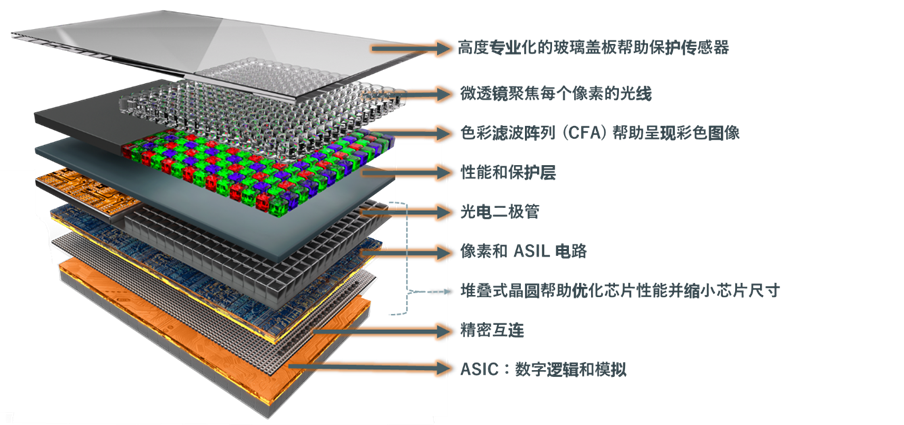

在技术创新的浪潮中,图像传感器的选型是设计与开发各类设备(涵盖专业与家庭安防系统、机器人、条码扫描仪、工厂自动化、设备检测、汽车等)过程中的关键环节。选择最适配的图像传感器需要对众多标准进行复杂的综合评估,每个标准都直接影响最终产品的性能和功能。从光学格式(Optical Format)和动态范围(Dynamic Range),到色彩滤波阵列(CFA)、像素类型、功耗及特性集成,这些考量因素多样且相互交织、错综复杂。

压控晶振(VCXO)作为频率调控的核心器件,已从基础时钟源升级为智能系统的"频率舵手"。通过变容二极管与石英晶体的精密耦合,实现电压-频率的线性转换,其相位噪声控制突破-160dBc/Hz@1kHz,抖动进入亚纳秒时代(0.15ps)。在5G-A/6G预研、224G光通信及自动驾驶多传感器同步场景中,VCXO正经历微型化(2016封装)、多协议兼容(LVDS/HCSL/CML集成)及温漂补偿算法的三重技术迭代。

在电子设备的精密计时体系中,晶体振荡器与实时时钟芯片如同时间系统的"心脏"与"大脑":晶振通过石英晶体的压电效应产生基础频率脉冲,为系统注入精准的"生命节拍";而实时时钟芯片则承担时序调度中枢的角色,将原始频率转化为可追踪的年月日时分秒,并实现闹钟、断电计时等高级功能。二者协同构建现代电子设备的"时间维度"。