发布时间:2025-12-23 阅读量:4021 来源: 发布人: suii

在电子系统设计中,晶振的性能参数直接决定了系统的稳定性和可靠性。从基准频率到工作电压,从输出电平到温度范围,每一个参数都承载着特定的技术含义和选型考量。

1、基准频率:

晶振在完全理想条件下的振荡频率。

2、工作电压:

晶振的工作需要外部提供一定的电源电压,晶振输出的时钟信号上的噪声与电源再说紧密相关,因此在晶振器件资料上,对电源的质量有一定的要求。

3、输出电平:

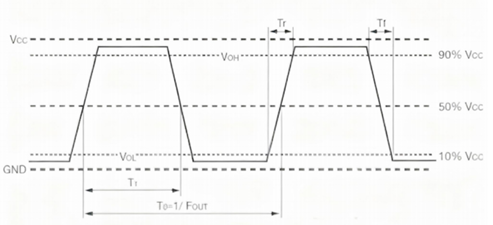

晶振与晶体相比,最为突出的一点就是只要上电,就直接输出时钟信号。时钟信号的电平也多种多样,支持的电平主要包括:TTL、CMOS、HCMOS、LVCOMS、LVPECL、LVDS等。在选型中,应根据所需时钟电平的种类选择相应的晶振。

4、工作温度范围:

根据环境温度要求的不同,应选择对应的工作温度范围。

5、频率精度:

对应不同的工作温度范围,可选择不同的频率精度。以±15ppm、-20~70℃为例,其含义是,在-20~70℃温度范围内,该晶振输出频率相对基准频率的偏差不会超过15ppm。该参数是晶振的重要参数,包含了由于温度变化、电源电压波动、负载变化等因素引起的频率偏差。

6、老化度:

在恒定的外接条件下测量晶振频率,频率精度与时间之间的关系。

7、启动时间:

从上电到晶振输出频率的偏差达到规定的频率精度所需要的时间。

8、时钟抖动(Jitter):

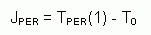

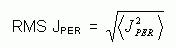

周期抖动(JPER)是实测周期与理想周期之间的时间差。由于具有随机分布的特点,可以用峰-峰值或均方根(RMS)描述。首先定义门限VTH的时钟上升沿位于时域的TPER(n),其中n是一个时域系统,如图所示。JPER表示为:

其中T0是理想时钟周期。由于时钟频率固定,随机抖动JPER的均值应该为零,JPER的RMS可表示为:

下图是周期抖动测量

利用示波器的边沿触发和余辉功能,可以粗略的测量信号的抖动。使用该方法的测量并不具有实际意义。(1)随着测量时间的增加,测得的抖动值将不断增加,即利用这种测量方法,无法得到确定的抖动值;(2)即使能得到确定的抖动值,这样的值对电路设计也没有任何指导意义,只能粗略判断所使用的晶振的抖动情况。

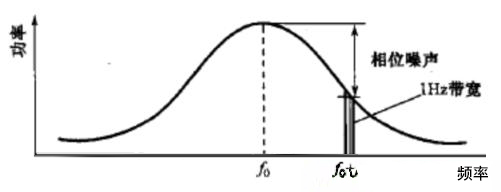

9、相位噪声:

在频域上,数据偏移量用相位噪声来定义。对于频率为f0的时钟信号而言,如果信号上不含抖动,则信号的所有功率应集中在频率点f0处,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。信号的相位噪声,就是信号在某一特定频率处的功率分量,将这些分量连接成的曲线就是相位噪声曲线。相位噪声通常定义为在某一给定偏移处的dBc/Hz值,其中dBc是以dB为单位的该功率处功率与总功率的比值。如一个振荡器在某一偏移频率处的相位噪声定义为在该频率处1Hz带宽内的信号功率与信号总功率的比值,即在fm频率处1Hz范围内的面积与整个噪声频率下的所有面积之比。

信号相位噪声曲线图

从相位噪声曲线图可知,绝大多数抖动都集中在频率f0附近,距离f0越远的频段,抖动能量越小。

以下面的例子为例,说明对时钟输入的要求:

RMS JPER(12kHz~20MHz):0.5ps

相位噪声(10~100kHz):-120dBc/Hz

这实际上是两个要求,一个是要求在频段12kHz~20MHz内,均方根抖动不能大于0.5ps;另一方面要求在频段10~100kHz内,任何频点处的功率谱密度都不能超过-120dBc/Hz。

晶振倍频干扰(即高次谐波辐射)是电磁兼容(EMC)设计中非常棘手的问题,通常表现为基频25MHz的5次、7次谐波(如125MHz、175MHz等)处辐射超标。该问题源于晶振输出方波信号包含丰富的高次谐波成分,若PCB布局不当,晶振及其走线极易构成高效辐射天线,导致电磁干扰增强。

提升石英晶体振荡器的相位噪声性能是一门融合材料学、机械设计与电子电路的系统工程,尤其在高速通信及精密测控领域,微小相位抖动就可能导致系统性能断崖式下跌。基于最新工业验证数据,我们总结出四种核心且硬核的优化方法,旨在从噪声源头系统性地帮工程师提升性能。

在光伏逆变器中,精确且稳定的时间不仅是数据记录的基础,更是系统运行、调度与运维的基础参数。

TCXO(Temperature Compensated Crystal Oscillator)是温度补偿晶体振荡器,通过集成热敏电阻和阻容元件构成的温度补偿电路,有效降低温度变化对振荡频率的影响。

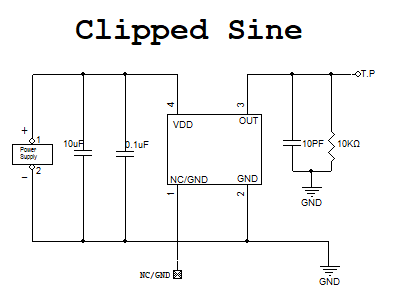

晶振(XO)的输出波形(Output Type)是衡量其性能的关键技术指标之一,其重要性不亚于封装尺寸。从技术角度区分,输出波形主要可分为正弦波和方波两大类。