发布时间:2026-01-21 阅读量:8640 来源: 发布人: suii

晶振倍频干扰(即高次谐波辐射)是电磁兼容(EMC)设计中非常棘手的问题,通常表现为基频25MHz的5次、7次谐波(如125MHz、175MHz等)处辐射超标。该问题源于晶振输出方波信号包含丰富的高次谐波成分,若PCB布局不当,晶振及其走线极易构成高效辐射天线,导致电磁干扰增强。

建议从源头抑制、路径切断到电路优化等以下几个方面解决:

一、优化PCB布局与布线(成本最低,最常用)

这是解决辐射问题的第一步,很多时候仅仅通过改板就能解决大部分问题。

· 包地处理(Guard Ring): 使用GND网络环绕晶振的信号线(特别是输出端),并在周围打一排接地过孔(Via)。这能切断信号向外辐射的路径,相当于给信号线加了一道“围墙”。

· 缩短走线长度: 晶振输出引脚到主芯片的走线必须尽可能短且直,避免走线过长形成天线效应辐射噪声。

· 底层挖空与铺地:

① 贴片晶振正下方的PCB层(尤其是表层)不能走其他信号线,最好将晶振下方的参考层(如地平面)进行适当的“挖空”处理,或者确保有完整的地平面作为回流路径。

② 如果晶振外壳需要接地,必须确保接地引脚与地平面的低阻抗连接。

· 远离敏感信号: 晶振走线应远离USB、网口、射频等高速或敏感信号线,防止串扰。

二、增加吸收与滤波电路(硬件整改)

如果改板来不及,或者需要进一步降低辐射,可以在电路中增加元件。

· 串联电阻/磁珠: 在晶振输出引脚串联一个0Ω~33Ω的小电阻(靠近晶振放置),可以抑制高频谐波的振荡,减小信号边沿的过冲和振铃,从而降低EMI。

· RC吸收电路: 在晶振输入/输出引脚对地增加一个RC低通滤波网络(例如串联10~100Ω电阻,对地并联10~100pF电容),可以吸收特定频段的谐振能量。

· 电源滤波: 在晶振的电源引脚(VCC)处,必须放置去耦电容(通常为0.1μF陶瓷电容),且电容要尽量靠近电源引脚。这能滤除电源线上的高频噪声,防止噪声通过电源线辐射。

三、更换晶振类型(源头治理)

如果电路板已经定型,无法修改走线,更换晶振型号是直接有效的办法。

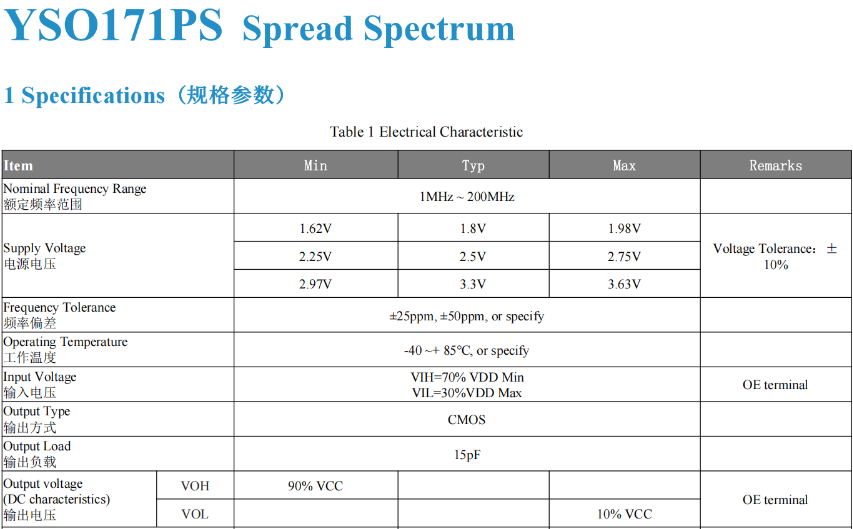

· 展频晶振(Spread Spectrum): 这种晶振通过微小的频率调制,将原本集中在单一频点的能量分散到一个频带范围内,从而大幅降低峰值辐射功率(通常可降低10dB以上)。

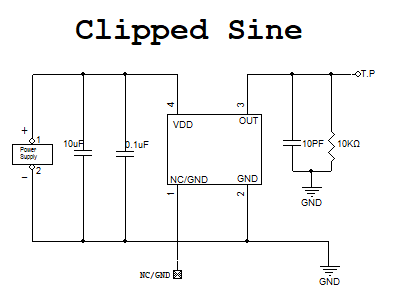

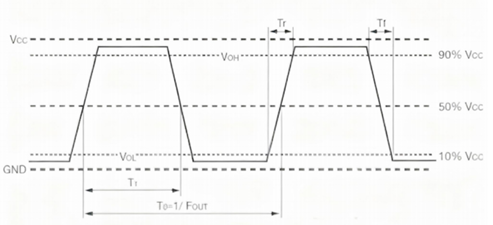

· 有源晶振(带使能端): 相比无源晶振,有源晶振输出波形质量更好(通常是方波或 clipped sine wave),且驱动能力强,受外围电路影响小,辐射特性通常优于无源晶振。

· 选择低EMI型号: 选购时关注晶振的相位噪声和谐波抑制指标,低相位噪声的晶振通常谐波能量也较低。

四、屏蔽与隔离(物理手段)

作为最后的大招,适用于辐射非常严重的场景。

· 加屏蔽罩: 使用金属屏蔽罩(Can)将整个晶振及其电路罩住,并确保屏蔽罩与PCB地平面有良好的低阻抗连接(四周打满过孔)。

· 单点接地: 对于无源晶振,确保其两个引脚的接地设计合理,避免地环路引入噪声。

总结来说,建议首先检查 PCB 上晶振周围是否已做好包地处理,这是最简便、成本最低且效果最显著的处理方法;如问题仍存,可考虑在晶振输出端串联小阻值电阻作为补充调试手段。

恒温晶振(Oven Controlled Crystal Oscillator,简称OCXO)是高精度频率源的核心组件,选用切型更优(如SC切、AT切高精度型)、封装应力极小的高Q值晶片,通过恒温槽的超精密控温,让晶振始终工作在零温度系数点,几乎消除温度引发的频率漂移。

提升石英晶体振荡器的相位噪声性能是一门融合材料学、机械设计与电子电路的系统工程,尤其在高速通信及精密测控领域,微小相位抖动就可能导致系统性能断崖式下跌。基于最新工业验证数据,我们总结出四种核心且硬核的优化方法,旨在从噪声源头系统性地帮工程师提升性能。

在光伏逆变器中,精确且稳定的时间不仅是数据记录的基础,更是系统运行、调度与运维的基础参数。

TCXO(Temperature Compensated Crystal Oscillator)是温度补偿晶体振荡器,通过集成热敏电阻和阻容元件构成的温度补偿电路,有效降低温度变化对振荡频率的影响。

晶振(XO)的输出波形(Output Type)是衡量其性能的关键技术指标之一,其重要性不亚于封装尺寸。从技术角度区分,输出波形主要可分为正弦波和方波两大类。