发布时间:2026-04-16 阅读量:101 来源: 发布人: suii

晶振作为电子设备的“心脏”,其核心作用是产生高稳定性的基准时钟信号。然而,其原始输出频率通常难以直接匹配系统中不同模块的工作需求——例如,处理器单元需要高频时钟以实现高速运算,而实时时钟等外围模块则依赖低频时钟来完成精准计时并降低系统功耗。

为了在性能与功耗之间取得最佳平衡,需要根据具体应用场景,对基准时钟进行相应的分频、倍频或转换处理,从而为各模块提供适宜的时钟信号。此时,分频技术就成为连接晶振基准频率与系统需求的关键,通过数字电路将晶振原始频率按固定比例降低,输出符合要求的低频时钟信号。

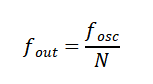

晶振分频的本质是通过数字分频电路(由触发器、计数器、锁相环等器件组成),对晶振输出的原始时钟信号进行“计数-翻转-输出”的逻辑操作,将高频信号按整数倍(或精准小数倍)降低为低频信号,核心遵循公式:

其中:为晶振原始输出频率(基准频率); 为分频后输出频率; 为分频系数(正整数或精准小数,由分频电路设计决定)。

分频的核心逻辑的是“周期性计数”:每接收 个原始时钟脉冲,分频电路输出1个脉冲,从而实现频率的等比例降低。根据实现方式,分频主要分为两类:

1.可编程分频:结合锁相环(PLL)与数字编程电路,可通过软件或硬件配置修改分频系数,支持多频点输出,灵活性强,适用于复杂系统。

2.硬件固定分频:由触发器、计数器等硬件器件组成固定逻辑,分频系数不可更改(如二分频、多级级联分频),结构简单、稳定性高,无额外误差。

关键注意点:分频仅改变时钟信号的频率(降低频率、延长周期),不改变信号的稳定性——晶振原始频率的精度(如温偏±25ppm)、稳定性,会100%传递到分频后的输出信号中,这也是高精度分频的核心前提。

典型案例1:可编程晶振的分频

可编程晶振(Programmable Oscillator,代表型号 YSO690PR、YSO212PU、YSO250PT)是一类灵活性极强的频率器件,核心通过固定基频晶体 + PLL 倍频 + 可编程分频的架构设计,支持工厂编程修改分频参数,可实现宽范围频率输出(最高达 2100MHz),且具备交货周期短的显著优势,凭借频点定制化、调试便捷性的特点,被广泛应用于工业控制、医疗电子、通信设备等对频率灵活性与交付效率有高要求的领域。

典型案例2:有源32.768kHz晶振的分频(高精度计时场景)

32.768kHz是RTC系统中最重要的频率,广泛应用于计时电路中,其核心需求是分频为1Hz秒脉冲,实现精准计时。市面上高精度(温偏±25ppm)的有源32.768kHz晶振,均采用“AT切MHz级基频晶片 + 专用数字分频IC(含振荡电路、整形电路、固定分频器)”的设计,将MHz级基频精准分频至32.768kHz,再输出标准方波(CMOS电平)。

为何不直接用AT切晶片做32.768kHz基频?因为AT切晶体的频率与晶片厚度成反比,32.768kHz基频对应的晶片厚度达数毫米,机械稳定性差、温漂无法做到±25ppm;而MHz级AT切晶片(如8MHz)厚度仅数十微米,工艺成熟、精度可控,分频后可完美继承其高精度特性。

32.768kHz分频至1Hz(RTC核心需求)

32.768kHz的特殊数值意义的是 ,因此可通过15级二分频电路,进一步分频至1Hz秒脉冲,实现精准计时:

每级二分频采用T触发器,每接收1个输入时钟上升沿,输出电平翻转一次,实现频率÷2;15级级联后,总分频系数为 ,最终输出1Hz方波(周期1s)。

典型应用:RTC芯片(如YSN8563,YSN8900),内部集成15级二分频电路,直接输出1Hz秒脉冲,驱动时间计数,可实现日历,闹钟,计数等功能。

按晶振的功能和实现技术的不同,分为温度补偿晶振(TCXO)、压控晶振(VCXO)、恒温晶振(OCXO)。

RTC芯片是一种专门用于精准计时、掉电续时的专用集成电路,其核心功能是提供精准、稳定的时间信息(包括秒、分、时、日、月、周、年),并能在主电源断电后依靠备用电池继续保持计时,从而确保时间持续不间断。

晶振的启动时间,通常是指其通电后进入稳定振荡状态所需的时间。若启动时间过长,可从以下五个常见的影响因素方面进行优化。

RTC(Real-Time Clock,实时时钟)芯片作为一种独立的专用计时器件,其核心功能包括提供稳定的日历时钟、在主电源断电后持续运行、支持定时中断以及输出高精度时间戳,为各类嵌入式系统提供可靠的时间基准。

时钟系统是保障微控制器(MCU)稳定运行的核心,而晶振作为关键时钟源,主要分为无源晶振与有源晶振两种类型。下面将围绕工作原理、硬件接口、电气特性及其在MCU中的适配场景等维度,系统解析这两类晶振与MCU之间的关联逻辑。