发布时间:2010-12-13 阅读量:3953 来源: 发布人:

【中心议题】

【解决方案】

1高速接口技术的发展趋势

近年来随着CPU/MPU的处理速度不断提高,对应于所处理数据的传输速度也越来越快;各种不断推陈出新的通信技术催生的高速接口的应用保证了数据的高速交互(见图1)。

.jpg)

同样,随着HDTV的发展,以HDMI接口为代表用于HDTV信号传输的高速接口更是成为各类高清数字电视必不可少的标准配置。并且随着HDMI1.4公布对于3D显示的支持(见图2),其展前途更加不可限量。

.jpg)

2高速接口芯片的发展趋势

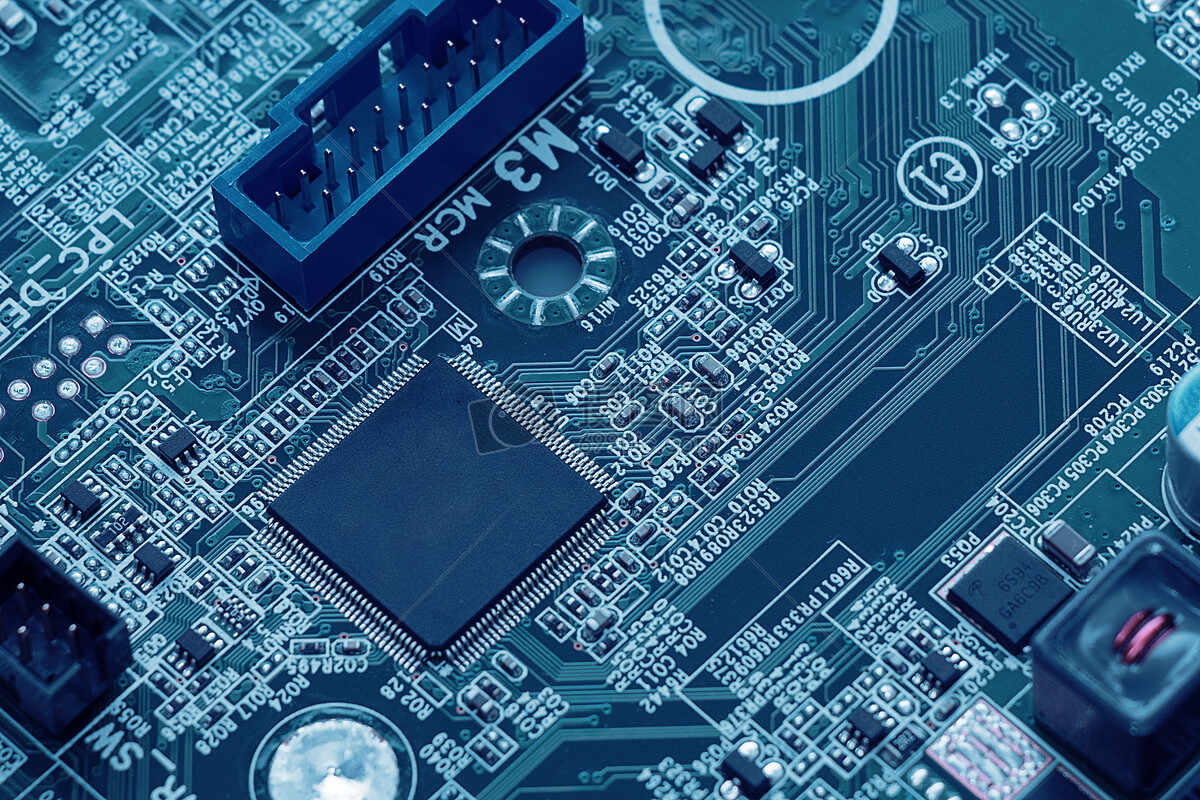

这些高速接口基本上都运用了SerDes技术(见图3),Serializer/Deserializer是目前以及未来较主流的串行数据传输方式。

.jpg)

PISO和SIPO大大降低对外接口的数量,使layout、互连等PCB、IC制造等方面的难度和成本大大降低。在一些高速数据传输的应用上,它与并行传输相比可以传送更高速率的数据。SerDes技术在65 nm工艺下已经可实现12 Gbps的应用(见表1)。

.jpg)

3高速接口芯片在ATE测试上面临的挑战

随着接口芯片传输速度的提高,如何充分验证其时序上的性能指标成为其在ATE上完成测试所必须解决的问题。主要有时钟恢复或时钟源同步、用于信道编码测试的大测试向量发生以及Jitter测试等问题。HDMI芯片工作原理见图4。

.jpg)

以图4中的HDMI芯片为例,其主要是以TMDS(Transition Minimized Differential Signaling,

即最小化传输差分信号)信号传输数据(见图5),根据数据通道数分为单路和双路。

.jpg)

HDMI一般使用单路TMDS信号,如何在数据传输速率最高达3.4 Gbps的情况下,保证3条数据通道的数据与时钟的10:1的同步关系,或者如何恢复时钟信息来同步检测高速数据成为一大难题。

高速接口测试经常使用的伪随机码(PRBS,Pseudorandom Bit Sequence)扰码长度随着位数的

增加以2的幂增长,测试向量也越来越大(见表2)。

.jpg)

由图6眼图可以得知在高速测试时Jitter对真实信号的影响愈发明显,所以如何衡量Tx产生信号的Jitter大小以及如何对用于Rx测试的信号中注入一定的Jitter考察Rx对Jitter的容忍情况成为ATE测试不可回避的问题。

.jpg)

4 ADVANTEST高速接口芯片测试解决方案

4.1 6 GSPM—6 Gbps Serial Port Module

面对高速接口芯片测试所面临的挑战,AD-VANTEST推出了高效低成本的6GSPM模块,其应用于开放式架构高性能SoC测试T2000上,为众多高速接口芯片的测试提供了高效低成本的测试解决方案(见图7)。

.jpg)

6GSPM提供了32对I/O分离的高速差分信号(16I/16O),最高可达6.375 Gbps。丰富的时钟同步及恢复模式,可对应于不同接口的不同要求灵活设置。、PRBS向量发生器和BERT(bit error rate tester单元解决了信道编码测试问题。眼图工具和Jitte注入功能的引入让在高速接口测试中越来越必不可少的Jitter相关测试得以轻松实现。

6GSPM对应于各种高速接口的时钟与数据同步格式要求,提供了设置灵活的时钟恢复和时钟源同步模式。上图就显示了源同步、转发时钟和内嵌时钟情况下6GSPM提供的应对方法。

此外时钟源的选择也很多样,除了系统时钟之外、芯片的输出及一些trig信号都可以用作同步使用的时钟源。图8就是一个HDMI Tx芯片测试的例子,其与数据通道同步的时钟源就是芯片本身的TMDS时钟信号。

6GSPM拥有专门的比特误码率测试单元(BERT,Bit Error Rate Tester)和高达31位伪随机码

(PRBS)向量发生器,满足了高速接口芯片的信道编码测试要求。

.jpg)

6GSPM对于Tx信号可以使用眼图工具获取其眼图特性数据,便于分析其信号的优劣。对于R芯片测试,有Jitter注入单元对系统输出信号注入一定量的抖动量对芯片进行测试,从而可以芯片对于抖动容许度这样一个在高速接口芯片测试上愈发重要指标的测试得以实现。

.jpg)

4.2 6GSPM与T2000SoC测试系统的结合

.jpg)

T2000是ADVANTEST推出的新一代开放式测试系统,其最大的特点是模块化结构,可以根据不同的DUT选配不同的测试模块,种类涵盖了DPS测试模块,数字测试模块、模拟测试模块、以及射频测试模块。上图就是T2000系统配置了DPS测试模块、低速800Mbps数字模块和6GSPM高速数字模块用于HDMI接口芯片测试的解决方案。

T2000除了自身提供了丰富的编程、调试用GUI用户工具,还支持各种新增模块的调试工具。GUI工具之间支持相互关联调用,调试时直观、人性化。

5降低高速接口芯片测试成本

为了降低测试成本,Advantest也从多方面考虑,用提高单位产能、降低模块价格、简化测试电路板设计过程等多个方法来尽可能减少分摊到单个芯片上的测试成本。

从6GSPM的设计来说,业界最多的16I/16O差分端口可以实现同样业界最高的HDMI 4port同测;而对于可以在低速情况下测得的DC参数,6GSPM通过32通道的SCAN/DC通路连接到其他低速数字模块(800MDM)进行测试,从而省去了高速数字模块的PMU单元,降低了模块的价格。

T2000的测试资源引出接口可以做到中心称排布,在设计测试电路板时可以只设计一个待

芯片(DUT)的布线,其余的三个可以对称使DUT1的布线设计,简化了设计过程。

6总结

ADVANTEST一直致力于开发最先进的测技术、并为客户提供完整的测试解决方案。现在

出新一代开放式架构的SoC测试系统T2000,并过不断开发新的模块来提高其测试能力,满足客数字、模拟、RF、高速接口等各种各样测试需求。

三星开启内部审查,严查员工收受不当回扣行为

长江存储正逐渐成为消费电子领域(包括PC与智能手机)为数不多的稳定供应来源。

据苏州高新区发布消息,12月18日,维谛技术华东研发制造基地战略合作项目签约仪式在苏州高新区举行。

由于半导体短缺,日本汽车大厂本田宣布实施短期停产与减产措施

近日,工业和信息化部部长李乐成在北京会见美国超威半导体公司(AMD)董事会主席兼首席执行官苏姿丰。