发布时间:2022-04-11 阅读量:1982 来源: 我爱方案网整理 发布人: Aurora

任何人对人工智能都有着自己的看法,而Mentor Graphics在今年夏天的DAC上讨论了关于AI的2个立场。作为一家EDA公司,他们有两个特定的机会来发现人工智能的价值。一是改进他们提供的设计工具;另一个是专门为人工智能设计创建设计工具。我们今天要讲第一个角度。

因此,对于这个故事,人工智能本身并不是终点;这将是达到目的的手段。人工智能已被用于生产车间,以帮助提高产量和减少设备损耗,但这依赖于晶圆厂的数据。今天,我们正从生产环境向设计领域的上游迈进。我们将特别关注Mentor如何利用人工智能在晶圆厂内进行光学邻近效应矫正(OPC)和制造设计(DfM)。

AI+OPC

让我们从OPC说起。对于任何新概念来说,由于硅尺寸太小,无法用光刻波长193nm打印,所以我们用了一些技巧。问题是,芯片特征尺寸如此之近,以至于影响了彼此形状的保真度。因此,这些形状被修改了——或者添加了“辅助功能”——以欺骗光线,让它照出我们想要的效果。

OPC通常使用确定性模型来完成,该模型允许工具创建修改后的模式。但Mentor表示,OPC面临四大挑战:

精度

周转时间(TAT)

工艺窗口增强

生产力

有两家公司运用了人工智能来解决这一问题。为了达到所需的精度,在24小时内完成OPC所需的内核数量正在急剧增加。他们把人工智能看作是一种降低这种风险的方法。

正如你从图中所看到的,24小时循环所需的核心数量下降了三分之二。另一种说法是,带有人工智能的TAT是传统方法的三分之一,同时提高了精确度。

用于训练模型的数据是基于最初的晶圆设计测量。为了确定整个工艺窗口,我们进行了实验设计(DoE)来扩展数据集,新的设计可以利用该模型进行OPC。

模型的演变

当然,人工智能的一个有趣的特点是永无止境的学习。得到的数据越多,模型就越好。因此,从理论上讲,人们可以在最初批量生产的基础上继续获取制造数据,并将其纳入人工智能模型中,以便随着时间的推移不断改进。

但这里有个问题。

假设你的流片设计已经搞定,但发现需要进行更改。当你激活工程变更命令(ECO)流程并进行调整时,它需要生成一个新的掩码,这就需要OPC的帮忙。

这样可以吗?你相信人工智能模型的进化只会改善这件事情吗?或者,你是否会以一些曾经有效的东西不再有效而告终?尽管有很多意想不到的事情发生了改变,但它变得更好了。但是现在是否需要运行一些测试来确保没有损坏?这违反了基本原则,“如果它没有坏,就不要修理它!”“那你该怎么处理呢?”

Mentor好像还没有一个拿得出手的方针。他们指出,当发现新的坏点时,首要任务是进行选择性的生产调整,以尽可能提高产量。但这种变化可以被应用到人工智能模型中,让它能够凸显出模具中更多的问题区域。因此,“持续学习”模式是切实可行的。

这也可以用OPC(或任何其他)AI模型来实现:将模型的版本锁定到设计中,以便将来对该设计所做的任何工作都将使用相同的AI模型。

综上所述,我觉得我们正在进入一个不稳定的领域,所以可能有一些法则规定了在这种情况下应该做什么。

首先,必须承认对于应用于哪个产品存在困惑。它看起来很像DRC,但实际上它是用于库验证的。换句话说,这不是一个你作为设计师会使用的工具;这是晶圆厂在组装电路库时使用的工具。是为了通过图案找到限制产量的坏点,而这些通常需要在一夜之间完成。

创新之处在于,他们不再使用库来进行谏检验,而是使用它来训练一个AI模型,然后使用AI模型来检出电路库。这带来了几个好处:首先,如果他们只使用库中的模型进行签出(checkout),那么你将只能在设计中找到那些特定的模式。但是,使用人工智能,可能会发现不在库中放其他类似的模式。所以得到了更好的质量和更高的产量。

另一个好处是,现在签出运行速度比使用传统模型快10倍。这种说法有一定的道理。进行完整的库模拟需要很长时间,这就是为什么签出常常限于特定的已知坏点。在抽样坏点时,覆盖范围并不全面。

延伸阅读

OPC技术背景

在半导体制造中,随着设计尺寸的不断缩小,光的衍射效应变得越来越明显,它的结果就是最终对设计图形产生的光学影像退化,最终在基底上经过光刻形成的实际图形变得和设计图形不同,这种现象被称为光学邻近效应(OPE:Optical Proximity Effect)。

为了修正光学邻近效应,便产生了光学邻近校正(OPC:Optical Proximity Correction)。光学邻近校正的核心思想就是基于抵消光学邻近效应的考虑,并建立光学邻近校正模型,根据光学邻近校正模型设计光掩模图形,这样虽然光刻后的光刻图形相对应光掩模图形发生了光学邻近效应,但是由于在根据光学邻近校正模型设计光掩模图形时已经考虑了对该现象的抵消。

坏点 Hot Spot

在集成电路制造中,经过OPC处理过的版图,在发送到掩模厂制造掩模之前,还需要进行验证,就是对OPC处理过的版图做仿真计算,确定其符合工艺窗口的要求。不符合工艺窗口要求的部分被称为坏点,坏点必须另行处理以符合工艺窗口的要求。

坏点修复

解决坏点的过程被称为“hot spot fixing”。在k1比较小的光刻层,第一次OPC处理后的坏点有十几万到几十万个。对坏点区域图形的审查和评估是一项浩繁的工作。坏点的解决一般由OPC工程师负责,通过调整OPC来解决。有些坏点是全局性的,通过修改OPC中的评价函数和规则,可以一起解决。而有些坏点有一定的特殊性,规则的改变会导致其他地方形成坏点。

常用的坏点解决办法示意

在任何数字电子系统中,时钟信号都扮演着“心脏起搏器”的角色。

RTC晶振与普通32.768kHz晶振的PCB设计要点基本一致,其核心均在于通过优化布线以降低杂散电容、确保频率精度,并依托合理的布局规划最大限度屏蔽来自板上其他信号源的电磁干扰。

按晶振的功能和实现技术的不同,分为温度补偿晶振(TCXO)、压控晶振(VCXO)、恒温晶振(OCXO)。

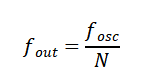

为了在性能与功耗之间取得最佳平衡,需要根据具体应用场景,对基准时钟进行相应的分频、倍频或转换处理,从而为各模块提供适宜的时钟信号。此时,分频技术就成为连接晶振基准频率与系统需求的关键,通过数字电路将晶振原始频率按固定比例降低,输出符合要求的低频时钟信号。

RTC芯片是一种专门用于精准计时、掉电续时的专用集成电路,其核心功能是提供精准、稳定的时间信息(包括秒、分、时、日、月、周、年),并能在主电源断电后依靠备用电池继续保持计时,从而确保时间持续不间断。