发布时间:2022-08-1 阅读量:2925 来源: 我爱方案网整理 发布人: Aurora

贴片电容是一种电容材质。贴片电容全称为:多层(积层,叠层)片式陶瓷电容器,也称为贴片电容,片容。贴片电容有两种表示方法,一种是英寸单位来表示,一种是毫米单位来表示。片式多层瓷介电容器(mlcc)简称片式电容器,是由印好电极(内电极)的陶瓷介质膜片以错位的方式叠合起来,经过一次性高温烧结形成陶瓷芯片,再在芯片的两端封上金属层(外电极),从而形成一个类似独石的结构体,故也叫独石电容器。

多层片式陶瓷电容器的结构主要包括三大部分:陶瓷介质,金属内电极,金属外电极。而多层片式陶瓷电容器它是一个多层叠合的结构,简单地说它是由多个简单平行板电容器的并联体。

贴片电容如何区分正负极

贴片电容又名SMD电容器、表面安装电容器,外表通常为黄色、玄色或淡蓝色。可分为无极性和有极性两类。现在主要探讨一下有极性贴片电容正负极区分。

贴片铝电解电容电容的正负极区分和丈量电容上面有标志的黑块为负极。在PCB上电容位置上有两个半圆,涂颜色的半圆对应的引脚为负极。也有用引脚是非来区别正负极长脚为正,短脚为负。

当我们不知道电容的正负极时,可以用万用表来丈量。电容两极之间的介质并不是绝对的绝缘体,它的电阻也不是无穷大,而是一个有限的数值,一般在1000兆欧以上。电容两极之间的电阻叫做绝缘电阻或漏电电阻。只有电解电容的正极接电源正(电阻挡时的黑表笔),负端接电源负(电阻挡时的红表笔)时,电解电容的漏电流才小(漏电阻大)。反之,则电解电容的漏电流增加(漏电阻减小)。这样,我们先假定某极为“+”极,指针式万用表选用R*100或R*1K挡,然后将假定的“+”极与万用表的黑表笔相接,另一电极与万用表的红表笔相接,记下表针休止的刻度(表针靠左阻值大),(对于数字万用表来说可以直接读出读数。)然后将电容放电(两根引线碰一下),然后两只表笔对调,重新进行丈量。两次丈量中,表针最后停留的位置靠左(或阻值大)的那次,黑表笔接的就是电解电容的正极。

贴片电容作用

1、去耦作用

电容在去耦电路中就叫做“去耦”电容,那么起到的作用自然也就是去耦作用了,主要是消除没记放大器见的耦合干扰以及输出信号的干扰。

2、中和作用

用于中和电路中的电容器叫中和电容,多用于收音机和电视机的高频放大器中,用来消除自激和震荡现象。

3、耦合作用

电容的耦合作用主要是为了防止前后两级电路的静态工作点相互影响,起的作用是通交流阻直流,这也是电容最重要的特性之一。

4、储能作用

说到储能歹意个想到的就是电池了,电子产品中的电池其实都是电容的一种,在电路中主要起到充放电的作用。

5、滤波作用

滤波是电容的作用中比较中要的一部分,几乎所有的电源电路中都会用到。电容越大低频就越容易通过,电容越小高频就越容易通过,因此可以得出容量大的贴片电容滤低频,容量小的电容器滤高频。

6、时间常数

时间常数是指过度反应所需要的时间,主要是控制时间常数的大小,从而控制电容充放电的时间。

关于我爱方案网

我爱方案网是一个电子方案开发供应链平台,提供从找方案到研发采购的全链条服务。找方案,上我爱方案网!在方案超市找到合适的方案就可以直接买,没有找到就到快包定制开发。我爱方案网积累了一大批方案商和企业开发资源,能提供标准的模块和核心板以及定制开发服务,按要求交付PCBA、整机产品、软件或IoT系统。更多信息,敬请访问http://www.52solution.com

在任何数字电子系统中,时钟信号都扮演着“心脏起搏器”的角色。

RTC晶振与普通32.768kHz晶振的PCB设计要点基本一致,其核心均在于通过优化布线以降低杂散电容、确保频率精度,并依托合理的布局规划最大限度屏蔽来自板上其他信号源的电磁干扰。

按晶振的功能和实现技术的不同,分为温度补偿晶振(TCXO)、压控晶振(VCXO)、恒温晶振(OCXO)。

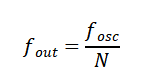

为了在性能与功耗之间取得最佳平衡,需要根据具体应用场景,对基准时钟进行相应的分频、倍频或转换处理,从而为各模块提供适宜的时钟信号。此时,分频技术就成为连接晶振基准频率与系统需求的关键,通过数字电路将晶振原始频率按固定比例降低,输出符合要求的低频时钟信号。

RTC芯片是一种专门用于精准计时、掉电续时的专用集成电路,其核心功能是提供精准、稳定的时间信息(包括秒、分、时、日、月、周、年),并能在主电源断电后依靠备用电池继续保持计时,从而确保时间持续不间断。