发布时间:2025-05-22 阅读量:1219 来源: 我爱方案网 作者:

【导读】2025年5月22日,电子设计自动化领域巨头Cadence正式发布HBM4内存IP解决方案,其数据传输速率达到业界领先的12.8Gbps,较前代HBM3E产品带宽翻倍。该方案基于JEDEC最新发布的JESD270-4规范,针对AI训练与高性能计算(HPC)系统的内存带宽需求进行了全面优化。

技术架构革新

Cadence HBM4解决方案包含物理层(PHY)与控制器IP,采用台积电N3及N2先进制程的嵌入式硬宏架构,面积效率提升50%,每比特能效提高20%。通过2048位接口与32通道设计,单堆栈容量可达64GB,总带宽突破2TB/s,较现有HBM4 DRAM设备性能提升60%。其RAS(可靠性、可用性、可维护性)功能与BIST(内建自测试)模块,可实时优化数据中心内存子系统性能。

生态系统协同创新

该方案已通过验证IP(VIP)实现快速收敛,支持DFI协议与系统级性能分析工具,配套的LabStation调试软件可将硅后验证周期缩短30%。值得关注的是,Cadence与台积电、三星等厂商在中介层设计上深度合作,其参考中介层方案已通过全功能测试芯片验证,为异构计算架构提供灵活部署可能。

行业影响与市场前景

随着生成式AI模型参数量突破万亿级,内存带宽已成为制约算力提升的关键瓶颈。Cadence芯片解决方案事业部总经理Boyd Phelps指出:"HBM4通过面积与功耗的同步优化,为AI工厂提供了面向未来的内存扩展路径。"目前,SK海力士、美光等存储厂商已加速HBM4量产进程,预计2025年下半年将配套英伟达新一代GPU实现商用。

4月2日,兆易创新宣布正式发布新一代SPI NAND Flash产品GD5F4GM7/GD5F8GM8。

标普全球Visible Alpha研究主管Melissa Otto指出,当前推动股市创纪录上涨的人工智能巨额投资正面临显著挑战,主要由于中东危机对全球经济增长前景与能源成本带来不确定性影响。

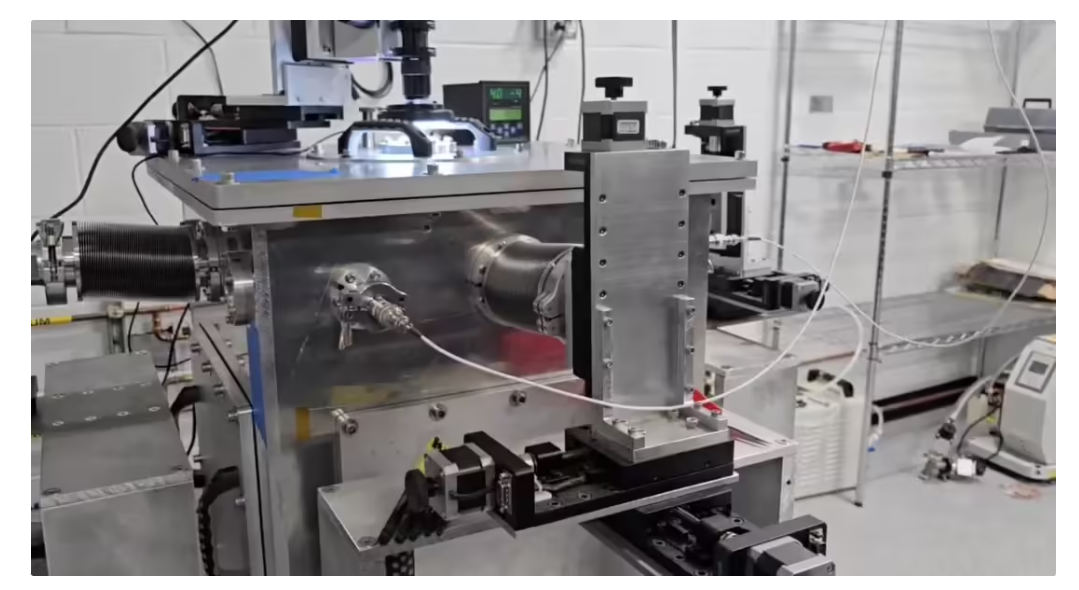

南加州大学团队研发新型存储芯片,可在 700°C 高温下稳定运行,且未出现性能退化迹象。

联发科和高通已开始下修于晶圆代工厂的4nm投片量,显示手机链景气明显降温

EM8695 RedCap模块基于Qualcomm SDX35基频处理器,为无需传统5G全速率或复杂功能的应用提供精简型5G解决方案